### INCREASING RENDERING PERFORMANCE OF GRAPHICS HARDWARE

Justin Hensley

A dissertation submitted to the faculty of the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

Chapel Hill 2007

Approved by: Anselmo Lastra Montek Singh Mary Whitton Leonard McMillan Steve Molnar

© 2007 Justin Hensley ALL RIGHTS RESERVED

## ABSTRACT

JUSTIN HENSLEY: Increasing Rendering Performance of Graphics Hardware (Under the direction of Anselmo Lastra and Montek Singh)

Graphics Processing Unit (GPU) performance is increasing faster than central processing unit (CPU) performance. This growth is driven by performance improvements that can be divided into the following three categories: algorithmic improvements, architectural improvements, and circuit-level improvements. In this dissertation I present techniques that improve the rendering performance of graphics hardware measured in speed, power consumption or image quality in each of these three areas.

At the algorithmic level, I introduce a method for using graphics hardware to rapidly and efficiently generate *summed-area tables*, which are data structures that hold pre-computed two-dimensional integrals of subsets of a given image, and present several novel rendering techniques that take advantage of summed-area tables to produce dynamic, high-quality images at interactive frame rates. These techniques improve the visual quality of images rendered on current commodity GPUs without requiring modifications to the underlying hardware or architecture.

At the architectural level, I propose modifications to the architecture of current GPUs that add conditional streaming capabilities. I describe a novel GPU-based ray-tracing algorithm that takes advantage of conditional output streams to reduce the memory bandwidth requirements by over an order of magnitude times when compared to previous techniques.

At the circuit level, I propose a *compute-on-demand* paradigm for the design of high-speed and energy-efficient graphics components. The goal of the compute-on-demand paradigm is to only perform computation at the bit-level when needed. The compute-on-demand paradigm exploits the data-dependent nature of computation, and thereby obtains speed and energy improvements by optimizing designs for the common case. This approach is illustrated with the design of a high-speed Z-comparator that is implemented using asynchronous logic. Asynchronous or "clockless" circuits were chosen for my implementations since they allow for data-dependent completion times and reduced power consumption by disabling inactive components. The resulting circuit-level implementation runs over 1.5 times faster while on dissipating 25% the energy of a comparable synchronous comparator for the average case.

Also at the circuit-level, I introduce a novel implementation of *counterflow pipelining*, which allows two streams of data to flow in opposite directions within the same pipeline without the need for complex arbitration. The advantages of this implementation are demonstrated by the design of a high-speed asynchronous Booth multiplier. While both the comparator and the multiplier are useful components of a graphics pipeline, the objective of this work was to propose the new design paradigm as a promising alternative to current graphics hardware design practices.

In memory of my brother, Jeff Hensley. As children we didn't always get along, and I regret not being able to tell you how much you meant to me. I love you and I miss you.

## ACKNOWLEDGMENTS

Ever since I can remember, I have always wanted to get my Ph.D. As a young child, I would often inform people that I was going to get my doctorate in aeronautical engineering. Since you are currently reading this dissertation, it should be fairly clear to you that I did not in fact get my Ph.D. in aeronautical engineering. If you are expecting a treatise on airplane design, you are gravely mistaken. Despite this minor change in plans, I have always known that I would be going to college, even from an early age. I believe that I have my parents to thank for this. There was never a question about whether I would go to college. My parents always supported me, and always wanted me to do my best, whatever it was that I chose to do. For their unwavering support, I would like to thank my parents.

My journey through college has been filled with some of the happiest times of my life, and some of the saddest times of my life. As an undergraduate, I was fortunate enough to live in a small dorm at the University of California at Davis. It is there that I met Ami, the love of my life, an amazing woman, who, when I asked her to marry me, said yes. She was willing to transfer universities in the middle of her veterinary medical program so that we could be together after the we got married. I know that it was difficult for Ami to leave her friends at Purdue to attend North Carolina State University, and for her sacrifice I am eternally grateful, since I know that I would not have been able to finish this dissertation without her support. For being there when it mattered most for me, thank you Ami. <sup>1</sup>

As an undergraduate, I originally started out in the biosystems engineering program at UC Davis. It did not take long, one quarter in fact, for me to decide that biosystem engineering was not for me. Suffice to say, the course that led to my decision involved learning about mass producing bean sprouts, and I have always known that I did **not** want to work in agriculture. Sorry dad. After filling out the requisite forms, I was soon majoring in computer science and

<sup>&</sup>lt;sup>1</sup>note to reader: despite my wife's protestations, I did not remove the preceding paragraph

electrical engineering. When I got my first introduction to computer graphics, I was well on my way to becoming a computer architect, but after taking "Introduction to Computer Graphics" with Professor Ken Joy, I knew that I wanted to work with computer graphics. I would like to thank Professor Joy for introducing me to the field of computer graphics, and for his encouragement to attend UNC for my doctorate degree.

At UNC, I initially joined the "Office of the Future" research group, and began working on what was eventually named PixelFlex. As a member of OOTF I was advised by Herman Towles and Henry Fuchs. I am grateful for the guidance they gave me during my first two years at UNC, but as fate would have it one tragic day I received a phone call that my brother had died. In a single moment, my life had changed forever. While I know it is trite to say that, there are no other ways I can describe how I felt on that day and how I still feel.

My co-advisors Montek Singh and Anselmo Lastra have been invaluable to me. All of the research I have done since leaving the PixelFlex project has been under their supervision. For the past four years, the endpoint of my research has not always been sight; Anselmo and Montek have been there to help me through the rough patches. For their support and guidance, I would like to thank my co-advisors.

To the rest of my committee, Leonard, Mary, and Steve: I would like to thank you for your advice and guidance. To my friends at UNC, thank you for the support and friendship you have given me. Finally, I would also like to thank the many foosball players in the department who helped me keep my sanity.

# TABLE OF CONTENTS

| $\mathbf{L}$ | IST ( | OF TABLES                                                                  | xiii |

|--------------|-------|----------------------------------------------------------------------------|------|

| L]           | IST ( | OF FIGURES                                                                 | xiv  |

| L]           | IST ( | OF ABBREVIATIONS                                                           | xvi  |

| 1            | Intr  | roduction                                                                  | 1    |

|              | 1.1   | The Algorithmic Axis: Improving Rendering Quality with GPU-Based Summed-   |      |

|              |       | Area Tables and Extensions                                                 | 2    |

|              |       | 1.1.1 Background                                                           | 3    |

|              |       | 1.1.2 Contributions                                                        | 5    |

|              | 1.2   | The Architectural Axis: Extending Graphics Architectures with Conditional  |      |

|              |       | Output Streams Increases Rendering Capabilities                            | 6    |

|              |       | 1.2.1 Conditional Streams                                                  | 8    |

|              |       | 1.2.2 Contributions                                                        | 8    |

|              | 1.3   | The Circuit Axis: Asynchronous Techniques for Improving the Efficiency and |      |

|              |       | Performance of GPUs                                                        | 9    |

|              |       | 1.3.1 Contributions                                                        | 10   |

|              | 1.4   | Thesis Statement                                                           | 11   |

|              | 1.5   | Major Contributions                                                        | 12   |

|              | 1.6   | Dissertation Organization                                                  | 14   |

| <b>2</b>     | Inc   | reasing Rendering Performance Along the Algorithmic Axis                   | 15   |

|              | 2.1   | Background                                                                 | 15   |

|              |       | 2.1.1 Reflection and Environment Mapping                                   | 16   |

|   |      | 2.1.1.1 Planar Reflection Mapping                                    | 6          |

|---|------|----------------------------------------------------------------------|------------|

|   |      | 2.1.1.2 Cube Mapping                                                 | 7          |

|   |      | 2.1.1.3 Dual-Paraboloid Mapping                                      | 7          |

|   |      | 2.1.2 High-Dynamic Range Images                                      | 9          |

|   |      | 2.1.3 Image-Based Lighting                                           | 9          |

|   | 2.2  | Summed-Area Tables                                                   | 21         |

|   |      | 2.2.1 Higher-Order Summed-Area Tables                                | 22         |

|   |      | 2.2.2 Related Techniques                                             | 23         |

|   |      | 2.2.3 Efficient Summed-Area Table Generation on GPUs                 | 23         |

|   |      | 2.2.4 Summed-Area Table Generation Performance                       | 27         |

|   | 2.3  | Offset Summed-Area Tables                                            | 29         |

|   |      | 2.3.1 Source of Precision Loss                                       | 29         |

|   |      | 2.3.2 Using Signed-Offset Pixel Representation                       | 81         |

|   | 2.4  | Higher-Order Summed-Area Table Generation    3                       | 32         |

|   | 2.5  | Rendering Glossy Reflections with Summed-Area Tables                 | 84         |

|   |      | 2.5.1 Glossy Environmental Reflections                               | 84         |

|   |      | 2.5.2 Glossy Planar Reflections                                      | <b>3</b> 9 |

|   | 2.6  | Depth-of-Field and Glossy Translucency                               | 39         |

|   |      | 2.6.1 Depth-of-Field                                                 | <b>3</b> 9 |

|   |      | 2.6.2 Translucency 4                                                 | 1          |

|   | 2.7  | Approximate HDR Image-Based Lighting 4                               | 2          |

|   | 2.8  | Conclusion                                                           | 15         |

| 3 | Inci | reasing Graphics Hardware Performance Along the Architectural Axis 4 | 6          |

| J |      |                                                                      |            |

|   | 3.1  |                                                                      | 18         |

|   |      | U U U U U U U U U U U U U U U U U U U                                | 19         |

|   |      | 3.1.2 Conditional Streams                                            | 9          |

|   |      | 3.1.3 Ray Tracing on GPUs                                            | 60         |

|   | 3.2  | Architectural Modifications                                          | 61         |

|   |      | 3.2.1 Decreasing Memory Fragmentation                                | 52         |

|   | 3.3  | Basic   | Streaming Ray Tracing Algorithm                        | 53 |

|---|------|---------|--------------------------------------------------------|----|

|   |      | 3.3.1   | Hybrid Algorithm                                       | 54 |

|   |      | 3.3.2   | Results                                                | 55 |

|   | 3.4  | Concl   | usion                                                  | 59 |

| 4 | Inci | reasing | g Graphics Hardware Performance Along the Circuit Axis | 60 |

|   | 4.1  | Backg   | round                                                  | 61 |

|   |      | 4.1.1   | Advantages of Asynchronous Design                      | 62 |

|   |      | 4.1.2   | Asynchronous Design Background                         | 62 |

|   |      |         | 4.1.2.1 Control Signaling                              | 63 |

|   |      |         | 4.1.2.2 Data Representation                            | 64 |

|   |      |         | 4.1.2.3 Completion Detection                           | 65 |

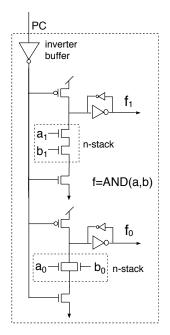

|   |      | 4.1.3   | Dynamic Logic                                          | 66 |

|   |      |         | 4.1.3.1 Energy Efficiency of Dynamic Logic             | 66 |

|   |      |         | 4.1.3.2 Structure and Implementation                   | 66 |

|   |      |         | 4.1.3.3 Operation                                      | 67 |

|   |      | 4.1.4   | Asynchronous Pipelining                                | 68 |

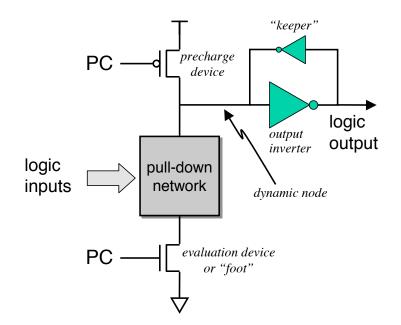

|   |      |         | 4.1.4.1 Overview                                       | 69 |

|   |      |         | 4.1.4.2 Williams' PS0 Pipeline Style                   | 69 |

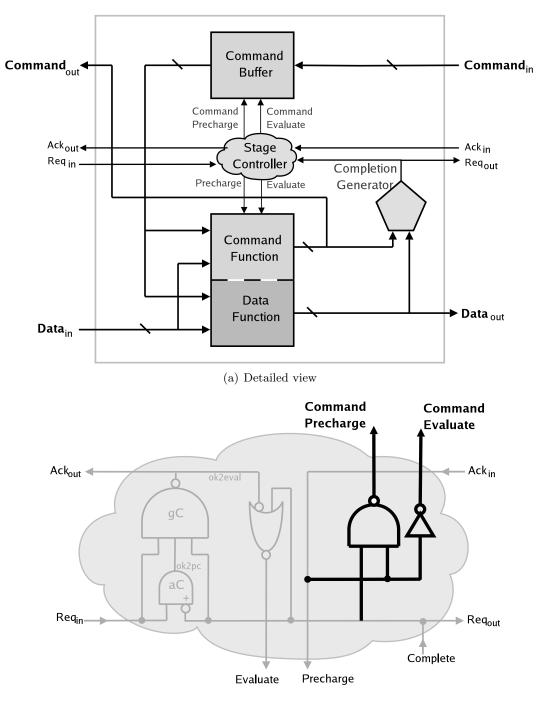

|   |      | 4.1.5   | Singh's High-Capacity Style Pipeline                   | 71 |

|   |      |         | 4.1.5.1 Motivation                                     | 71 |

|   |      |         | 4.1.5.2 Overview                                       | 72 |

|   |      |         | 4.1.5.3 Structure                                      | 72 |

|   |      |         | 4.1.5.4 Implementation                                 | 73 |

|   |      |         | 4.1.5.5 Operation                                      | 73 |

|   |      |         | 4.1.5.6 Performance                                    | 74 |

|   |      | 4.1.6   | Power-Performance Trade-Off, and the $E\tau^2$ Metric  | 74 |

|   | 4.2  | Comp    | ute-on-Demand Paradigm                                 | 75 |

|   |      | 4.2.1   | Previous Work                                          | 76 |

|   |      | 4.2.2   | Asynchronous Comparator                                | 78 |

|   |     |        | 4.2.2.1 Comparator Architecture                                                                                                               |

|---|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|   |     |        | 4.2.2.2 Comparator Operation: Compute-on-Demand                                                                                               |

|   |     | 4.2.3  | Experimental Results                                                                                                                          |

|   | 4.3 | High-( | Capacity Counterflow Pipelines                                                                                                                |

|   |     | 4.3.1  | Related Work                                                                                                                                  |

|   |     | 4.3.2  | Multiplier Design                                                                                                                             |

|   |     | 4.3.3  | Multiplier Architecture                                                                                                                       |

|   |     |        | 4.3.3.1 Overview                                                                                                                              |

|   |     |        | 4.3.3.2 Novel Counterflow Organization                                                                                                        |

|   |     |        | 4.3.3.3 Architectural Optimization: Folding Arithmetic Unit into Shifter 8                                                                    |

|   |     |        | 4.3.3.4 Command Representation                                                                                                                |

|   |     |        | 4.3.3.5 Data Representation                                                                                                                   |

|   |     | 4.3.4  | Operation                                                                                                                                     |

|   |     |        | $4.3.4.1  \text{Initialization}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                             |

|   |     |        | $4.3.4.2  \text{Execution} \dots \dots$ |

|   |     |        | 4.3.4.3 Termination                                                                                                                           |

|   |     |        | 4.3.4.4 Initialization (next round of computation) 92                                                                                         |

|   |     |        | 4.3.4.5 Overlapped Execution of Consecutive Computations 92                                                                                   |

|   |     | 4.3.5  | Implementation                                                                                                                                |

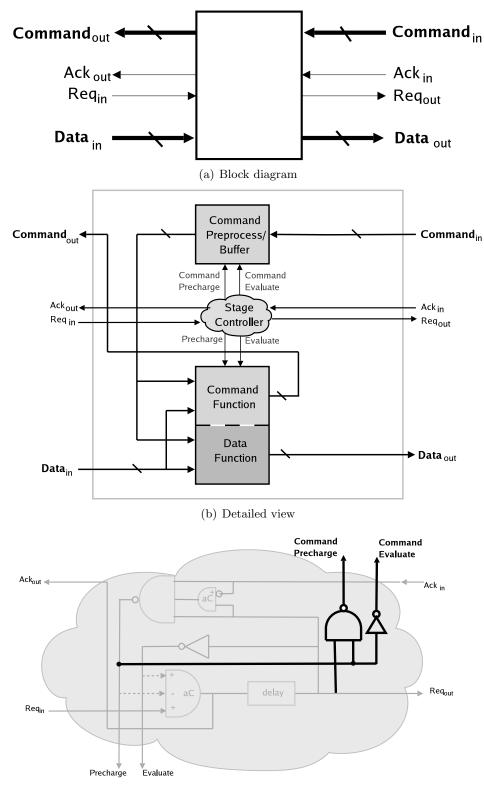

|   |     |        | 4.3.5.1 Pipeline Handshake Circuits                                                                                                           |

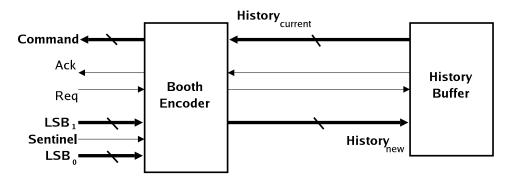

|   |     |        | 4.3.5.2 Booth Controller                                                                                                                      |

|   |     | 4.3.6  | Spice Simulation Results                                                                                                                      |

|   |     | 4.3.7  | Dynamic Precision-Energy Trade-Off                                                                                                            |

|   | 4.4 | Dual-I | Rail High-Capacity Counter-flow Pipelines                                                                                                     |

| 5 | Sun | nmary  | and Conclusion 99                                                                                                                             |

|   | 5.1 | , i    | thmic Axis                                                                                                                                    |

|   |     | 0      | 5.1.0.1 Contribution $\dots \dots \dots$      |

|   |     |        | 5.1.0.2 Future Work                                                                                                                           |

|   | 5.2 | Archit | ectural Axis                                                                                                                                  |

|     | 5.2.0.3         | Contribution . |  |  |  | • | • |  | • | • | • | • | • | • | • | • | • | <br>• | 101 |

|-----|-----------------|----------------|--|--|--|---|---|--|---|---|---|---|---|---|---|---|---|-------|-----|

|     | 5.2.0.4         | Future Work .  |  |  |  | • | • |  | • | • | • | • |   | • |   | • | • |       | 102 |

| 5.3 | Circuit-Level A | xis            |  |  |  |   | • |  | • | • |   | • |   | • |   | • | • |       | 102 |

|     | 5.3.0.5         | Contribution . |  |  |  | • | • |  | • | • | • | • |   | • |   | • | • |       | 102 |

|     | 5.3.0.6         | Future Work .  |  |  |  | • |   |  | • | • | • | • |   |   |   | • | • |       | 103 |

|     |                 |                |  |  |  |   |   |  |   |   |   |   |   |   |   |   |   |       |     |

### BIBLIOGRAPHY

# LIST OF TABLES

| 2.1 | Shortest time to generate summed-area tables of different sizes $\ldots \ldots \ldots$ | 28 |

|-----|----------------------------------------------------------------------------------------|----|

| 2.2 | Time to generate summed-area tables using different number of samples per pass         | 28 |

| 3.1 | Comparison of our technique with the results presented by Foley and Sugerman           | 56 |

| 3.2 | Scatter performance using GL_POINTS with a vertex shader on an ATI X1900XT $$          | 59 |

| 4.1 | 24-bit Comparator results                                                              | 80 |

## LIST OF FIGURES

| 1.1  | Sampling from summed-area tables                                                  | 4  |

|------|-----------------------------------------------------------------------------------|----|

| 1.2  | Glossy environmental reflections using summed-area tables                         | 5  |

| 1.3  | Conditional operations with streaming architectures                               | 7  |

| 1.4  | Synchronous and asynchronous system block diagrams                                | 10 |

| 1.5  | Distribution of z-comparison compute chain length                                 | 11 |

| 2.1  | Planar reflection mapping                                                         | 16 |

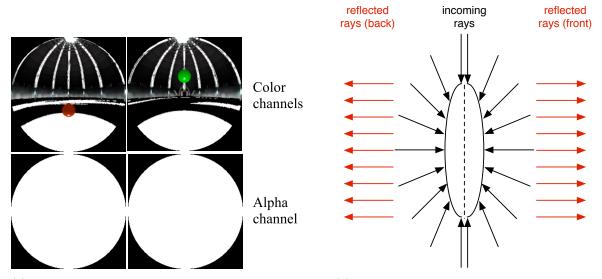

| 2.2  | Dual-paraboloid maps                                                              | 18 |

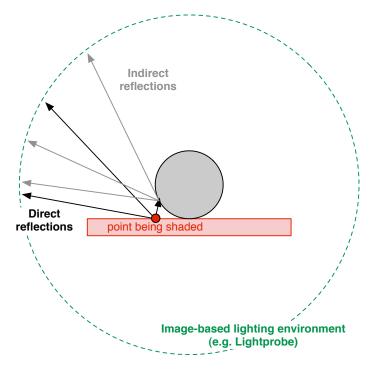

| 2.3  | Image-based lighting                                                              | 20 |

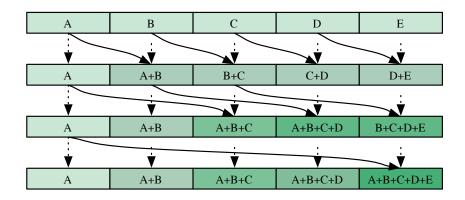

| 2.4  | The recursive doubling algorithm in 1D                                            | 24 |

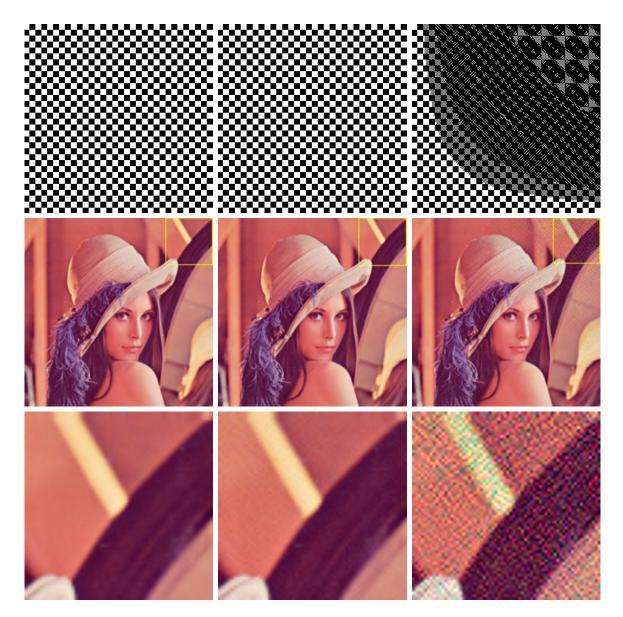

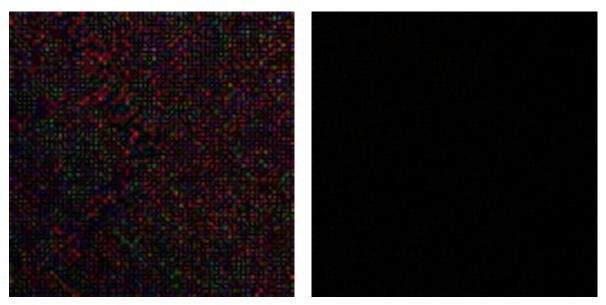

| 2.5  | Effects of precision loss with summed-area tables                                 | 30 |

| 2.6  | Summed-area table reconstruction error                                            | 32 |

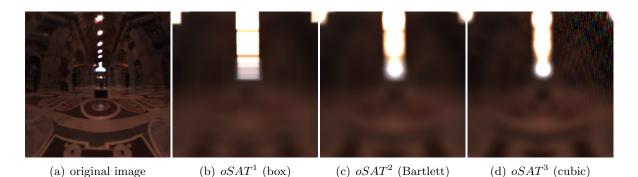

| 2.7  | Comparison of images filtered using repeated offset summed-area tables $\ldots$   | 33 |

| 2.8  | An object rendered with glossy reflections by filtering a dynamic environment     |    |

|      | map with a spatially varying kernel size                                          | 35 |

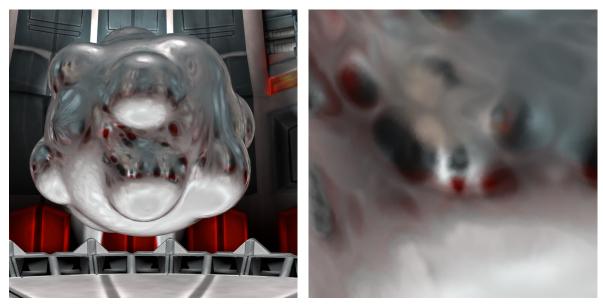

| 2.9  | An object textured using four samples from a pair of summed-area tables $\ . \ .$ | 36 |

| 2.10 | A set of four box filters stacked to approximate a Phong BRDF                     | 37 |

| 2.11 | An image illustrating the use of a summed-area table to render glossy planar      |    |

|      | reflections                                                                       | 38 |

| 2.12 | Simulated depth-of-field effect using summed-area tables                          | 40 |

| 2.13 | Example of translucency using a summed-area table                                 | 41 |

| 2.14 | Approximate image-based lighting computed from two sets of summed area            |    |

|      | tables                                                                            | 43 |

| 2.15 | Approximating a diffuse BRDF using summed area tables                             | 44 |

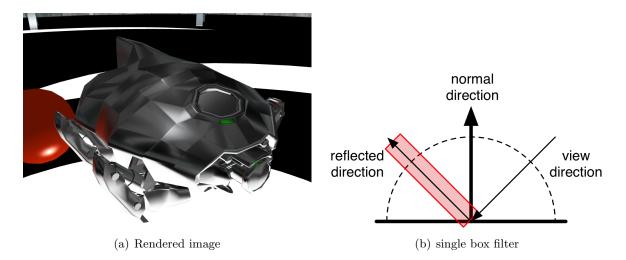

| 3.1  | Ray traced second generation rays using conditional output streams $\ldots$ .     | 47 |

| 3.2  | Conditional operations with streaming architectures                               | 50 |

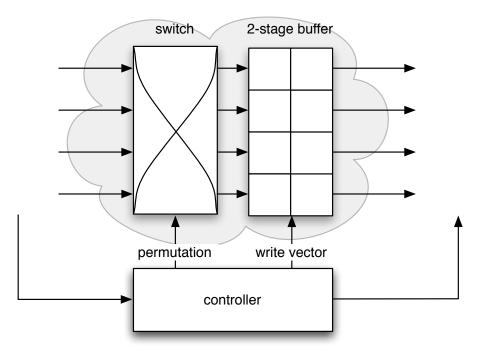

| 3.3  | Conditional output streams for graphics hardware                                  | 51 |

| 3.4  | Additional hardware needed to implement conditional streams in graphics   |    |

|------|---------------------------------------------------------------------------|----|

|      | hardware                                                                  | 52 |

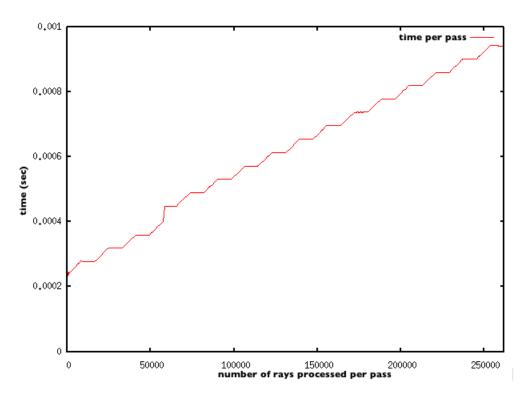

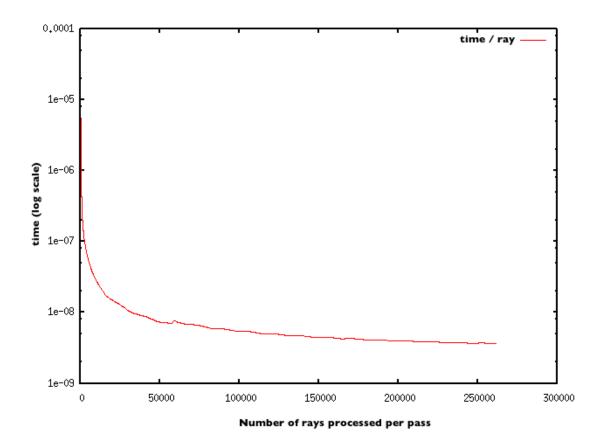

| 3.5  | Processing time per pass for kd-tree node traversal GLSL shader           | 57 |

| 3.6  | Effective processing time per ray for traversal shader                    | 58 |

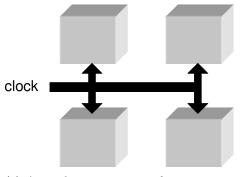

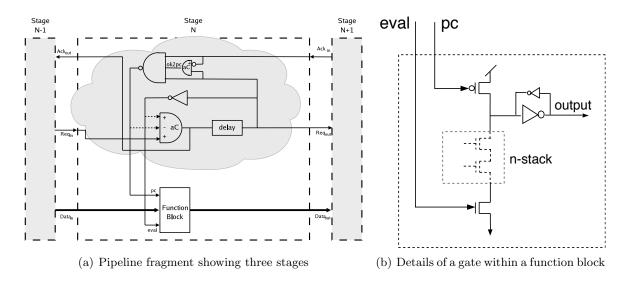

| 4.1  | Synchronous and asynchronous systems (figure adapted from (Singh, 2001)). | 61 |

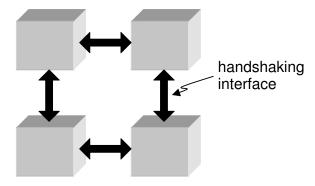

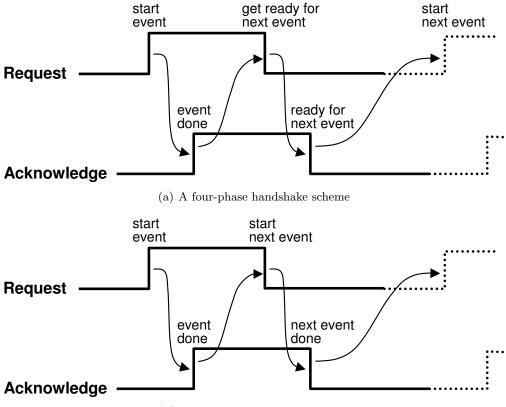

| 4.2  | Examples of handshake schemes                                             | 63 |

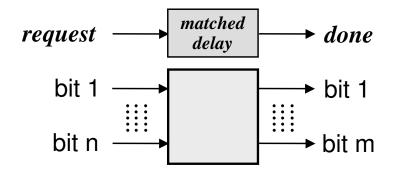

| 4.3  | A bundled data function block                                             | 64 |

| 4.4  | A dual-rail data encoding scheme                                          | 65 |

| 4.5  | A dual-rail AND gate in dynamic logic                                     | 67 |

| 4.6  | A dynamic logic gate (figure adapted from (Singh, 2001))                  | 68 |

| 4.7  | Block diagram of a PS0 pipeline                                           | 69 |

| 4.8  | The high-capacity (HC) pipeline style                                     | 71 |

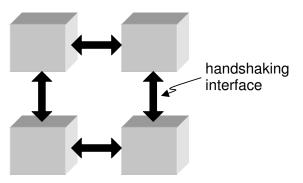

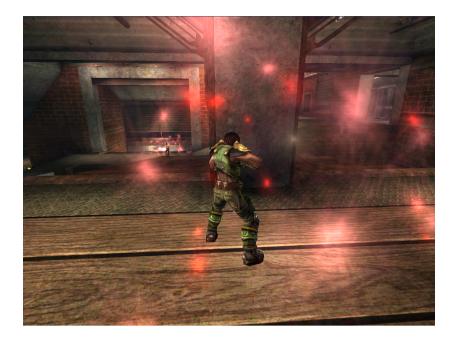

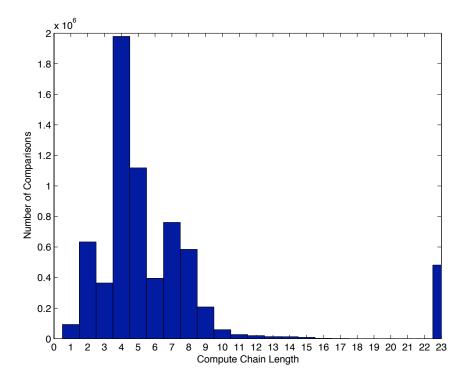

| 4.9  | A frame from Unreal Tournament 2004                                       | 76 |

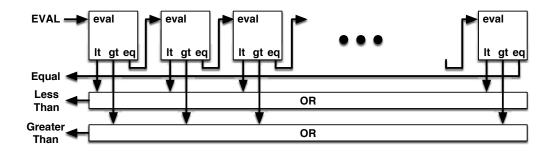

| 4.10 | A novel "compute-on-demand" comparator                                    | 79 |

| 4.11 | Distribution of z-comparison compute chain length for the frame shown in  |    |

|      | Figure 4.9                                                                | 81 |

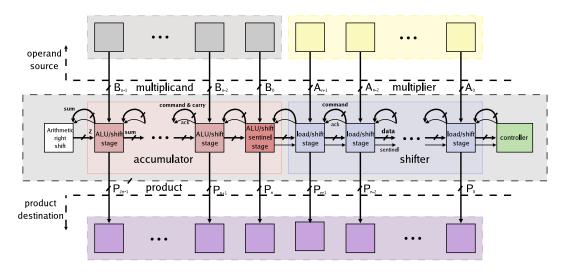

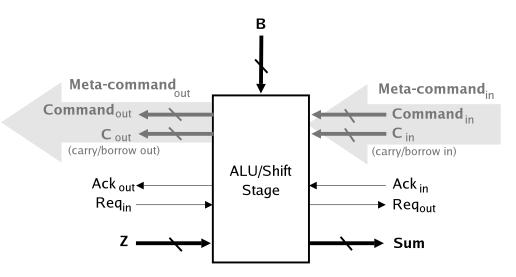

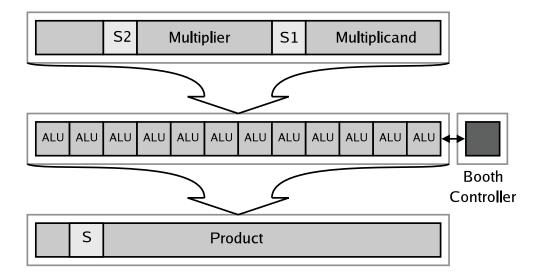

| 4.12 | The counterflow Booth multiplier                                          | 85 |

| 4.13 | The merged arithmetic/shift unit                                          | 88 |

| 4.14 | Pipeline Handshake Controller                                             | 90 |

| 4.15 | Booth Controller                                                          | 94 |

| 4.16 | Booth commands                                                            | 94 |

| 4.17 | The variable-precision Booth multiplier architecture                      | 96 |

| 4.18 | Pipeline Handshake Controller                                             | 98 |

# LIST OF ABBREVIATIONS

| Two-Dimensional              |

|------------------------------|

| Three-Dimensional            |

| Central Processing Unit      |

| Dynamic Random Access Memory |

| Graphics Processing Unit     |

| High-Capacity                |

| High-Capacity Counterflow    |

| High Dynamic Range           |

| Low Dynamic Range            |

| Pre-charge                   |

|                              |

#### CHAPTER 1

## Introduction

Graphics Processing Unit (Graphics Processing Unit (GPU)) performance is increasing faster than Central Processing Unit (Central Processing Unit (CPU)) performance, and is reported by some to be growing at a "Super-Moore's Law" rate (Govindaraju et al., 2006). This growth is driven by performance improvements that can be divided into the following three categories.

- Algorithmic: Algorithmic improvements are often initially implemented at the application level, using the current capabilities of current hardware. The relatively recent introduction of programmable pipelines to commodity GPUs enables a wide variety of algorithms to be implemented without architectural changes.

- Architectural: There are situations where a new algorithm lends itself to an efficient, direct implementation in hardware that would require only minimal changes to the GPUs architecture. For example, various environment mapping techniques initially required the application developer to handle texture coordinate generation, whereas modern GPUs are able to automatically transform normal and reflection directions into texture coordinates.

At the architectural level, enhancements designed to introduce new functionality or increase performance should be made without impacting the performance of legacy applications. This is an especially important property for devices destined for established commodity markets. For better or worse, the driving forces behind the commodity GPU market are video games, and it would be considered unacceptable for a newly released GPU to run slower on the current "game-de-jour" than the previous generation of products. • *Circuit:* At the circuit level, it is possible to make dramatic changes to the underlying circuitry without modifying the GPU's architecture or the application programmer interface. Some of the possible benefits of circuit-level modifications include faster computation, lower energy-consumption, or improved yields when fabricating integrated circuits. For example, some modern hardware has moved from using standard-cell implementations to custom ASICs without requiring changes to the overall architecture. Also, over the lifetime of a specific architecture, multiple different fabrication processes might be used — e.g. a device might initially be implemented in a 90 nm process, but later be fabricated in a 65 nm process as the architecture and fabrication processes become more mature.

Performance improvements can be measured in several ways. In this work I use metrics related to the visual image quality, speed of computation, and energy-efficiency. The following sections give more detail about the contributions made in these three areas.

## 1.1 The Algorithmic Axis: Improving Rendering Quality with GPU-Based Summed-Area Tables and Extensions

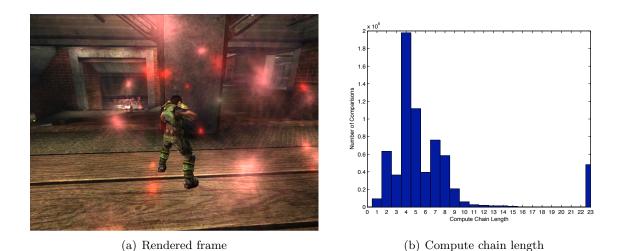

At the algorithmic level, I will discuss several novel techniques that are capable of improving the visual quality of images rendered on current commodity GPUs without requiring modifications to the underlying hardware or architecture. In particular, I will describe a method for using graphics hardware to rapidly and efficiently generate *summed-area tables*, which are data structures that hold pre-computed integrals of a given image. Additionally, I will describe extensions to summed area tables that reduce their precision requirements and present multiple rendering techniques that take advantage of summed-area tables to produce highquality images in real-time. My algorithm is able to compute a 256x256 summed-area table in less than 2ms, and render complex scenes, such as the one shown in Figure 1.2(a), with interactive glossy reflections at over 60 frames per second on relatively old hardware such as a Radeon X800XT PE.

The following quick tutorial is intended for readers unfamiliar with texture mapping and

summed-area tables. Readers familiar with the topics can skip to Section 1.1.2.

#### 1.1.1 Background

*Texture mapping*, a technique that is ubiquitous in computer graphics, is a process that enables simple rendered surfaces to appear to have complex surface properties. In its simplest form, texture mapping can be thought of as an image being used as a decal on the surface of an object. Introduced by Catmull (Catmull, 1974), texture mapping is a process whereby positions in three-space are mapped to an n-dimensional, parametric space, which allows for easy sampling of data stored in n-dimensional arrays such as images (2D) and volumetric data (3D).

As with any sampling technique, it is often necessary to filter or interpolate the data sampled from a texture map to attain visually pleasing images. In practice, it is cost-prohibitive to directly interpolate the texture map with anything more complex than linear interpolation. *Mipmaps* (Williams, 1983) address this issue by pre-computing multiple images, which are scaled-down versions of the original input image, and then performing trilinear interpolation between two levels of the mipmap.

First introduced by Crow (Crow, 1984), summed-area tables enable more general texture filtering than is possible with the commonly-used mipmapping technique. In particular, summed-area tables are able to more accurately reflect the data actually inside a box filter kernel at a specific location, whereas a nearby samples from a mipmap are limited to the average of a fixed set a pixels. When using a mipmap to perform more generalized filtering, this becomes apparent as visual defects in the filtered image. Although introduced at roughly the same time as mipmaps, summed-area tables have a more stringent precision requirement than an equivalently sized mipmap. Partly due to this limitation of summed-area tables, mipmapping became a more attractive technique to implement in early GPUs, and summedarea tables fell out of favor in real-time rendering. But, summed-area tables remained a useful technique in offline rendering applications such as the renders used in the film industry. The relatively recent availability of floating-point capable datapaths, and the associated increase in the available computational precision on commodity GPUs has facilitated a resurrection in

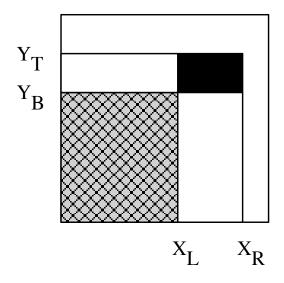

Figure 1.1: (after [Crow84]) An entry in the summed-area table holds the sum of the values from the lower left corner of the image to the current location. To compute the sum of the dark rectangular region, evaluate  $T[X_R, Y_T] - T[X_R, Y_B] - T[X_L, Y_T] + T[X_L, Y_B]$  where T is the value of the entry at (x, y).

the use of summed-area tables in real-time graphics, despite their high precision requirements.

For an image, a summed-area table is a two-dimensional array where each entry in the array stores the discrete integral for each rectangular sub-image of the input image. Summed-area tables enable at a fixed computational cost the rapid calculation of the sum of the pixel values in an arbitrarily sized, axis-aligned rectangle. Figure 1.1 illustrates how a summed-area table is used to compute the sum of the values of pixels spanning a rectangular region. To find the integral of the values in the dark rectangle, we begin with the pre-computed integral from (0,0) to  $(x_R, y_T)$ . We subtract the integrals of the rectangles (0, 0) to  $(x_R, y_B)$  and (0, 0) to  $(x_L, y_T)$ . The integral of the hatched box is then added to compensate for having been subtracted twice. Finally, the average value of a group of pixels can be calculated by dividing the sum by the area.

Once generated, a summed-area table provides a means to evaluate a spatially varying box filter with a constant number of memory accesses. For example, the average value of a 100x100 pixel region of an image could be computed with only four accesses to a summed-area table, whereas if the region were to be directly filtered, it would take 10,000 accesses to the original image. Summed-area tables were later extended by Heckbert (Heckbert, 1986) to

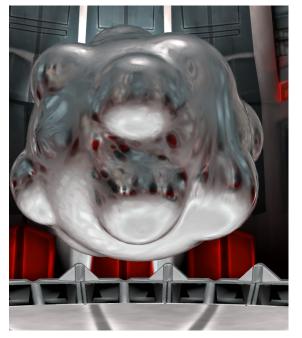

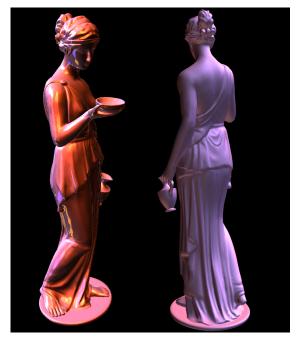

(a) Glossy environmental reflections

(b) Approximate HDR image-based lighting

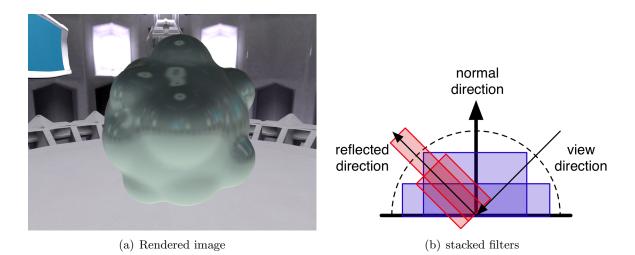

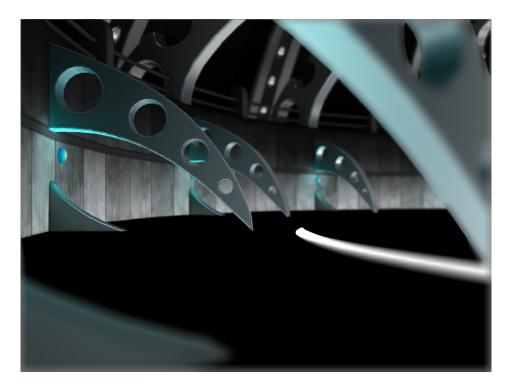

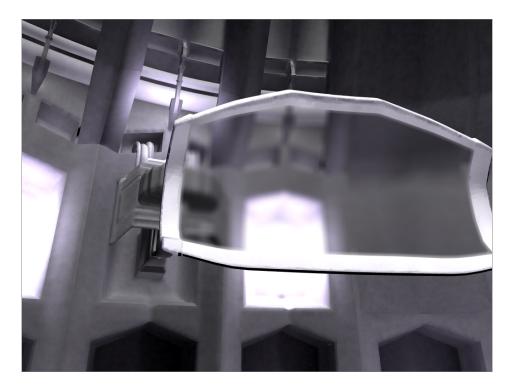

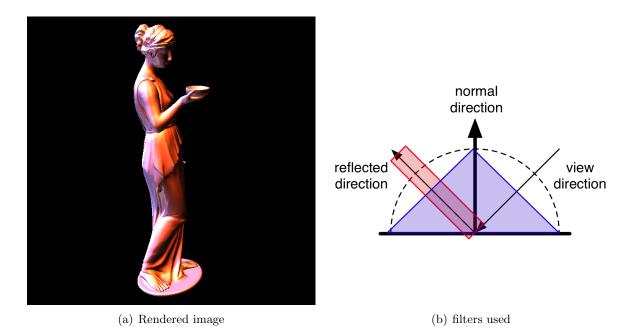

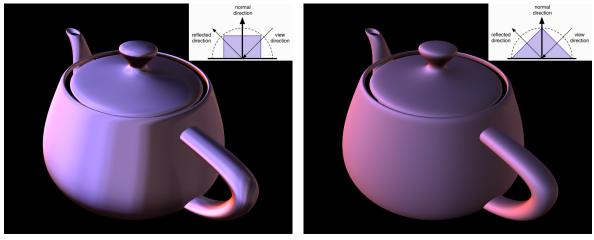

Figure 1.2: Image (a) shows an object rendered in real-time with an environment map filtered by a spatially varying filter. Image (b) shows A real-time rendering of a statue of Hebe, the Greek goddess of youth. All lighting calculations are only performed by sampling summed-area tables computed from the Grace Cathedral lightprobe (lightprobe courtesy of Paul Debevec). The left image of Hebe shows an approximation to the Phong BRDF, and the right image shows an approximation to a diffuse BRDF.

handle complex filter functions by taking advantage of the properties of convolution. These extensions will be described in more detail in Chapter 2.

### 1.1.2 Contributions

In this dissertation I present a method to rapidly generate summed-area tables that is efficient enough to allow multiple summed-area tables to be generated every frame while maintaining interactive frame rates. I extend the traditional summed-area table algorithm to reduce their precision requirements, which enables summed-area tables to easily be used on graphics hardware with relatively limited-precision, or alternatively, larger summed-area tables to be generated with visual artifacts being introduced. I demonstrate the applicability of spatially varying filters for real-time, interactive computer graphics through several different applications. Some example applications are the interactive rendering of dynamic glossy reflections (Hensley et al., 2005), and dynamic image-based lighting (Hensley et al., 2006). Figure 1.2(a) shows an image captured from a real-time application that is rendering an object with spatially varying glossy environmental reflections, while Figure 1.2(b) shows an image captured from a real-time application that is rendering a statue illuminated using an approximate image-based lighting technique. Using the metrics described earlier, these contributions improve rendering performance in two key ways: (i) improving the visual quality of rendered images, and (ii) increasing the speed of computing summed-area tables.

# 1.2 The Architectural Axis: Extending Graphics Architectures with Conditional Output Streams Increases Rendering Capabilities

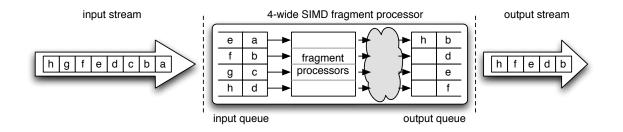

As with most data-parallel architectures, conditional operations are difficult to handle efficiently on graphics processors. This inefficiency arises because data-parallel architectures typically execute the same operation on multiple elements of data at the same time. This mode of operation is often referred to as SIMD — Single Instruction, Multiple Data. Since all the elements are operated on by the same instruction, data that requires separate branch paths forces redundant execution. In the worst case each element requires a different path through the code, forcing sequential operation instead of parallel operation, which is clearly undesirable.

GPUs are just now gaining conditional operations but because of a GPU's SIMD nature, they are limited to either consecutive arithmetic operations with no branching, or the inefficient execution of all of the possible branch outcomes for all pixels that executed together. As an example, ATI's X1800 shader architecture (ATI Technologies, 2005) processes sixteen pixels in parallel. The X1800 is optimized to take advantage of the situation where all pixels branch the same way, otherwise both paths of the branch would require execution (although, this optimization only helps where there is large amount of locality to the branching pattern). For example, consider the following shader pseudo-code:

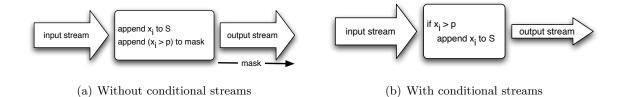

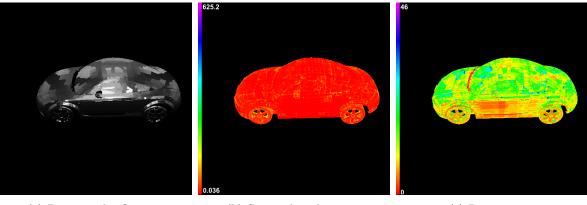

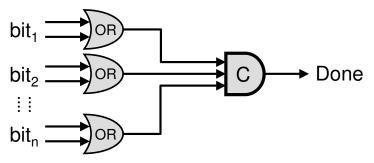

Figure 1.3: Conditional operations with streaming architectures. Figure (a) shows how a mask must be used to prevent downstream compute kernels from operating on invalid data. The output stream is the same size as the input stream, and the mask has the same number of elements as the input stream. Figure (b) shows the same simple conditional operation with conditional output streams. In this situation, the output stream is only as large as it needs to be, no additional mask vector is needed, and processor utilization of downstream kernels is increased.

if pixel not in shadow then

```

computeLighting()

```

else

```

computeShadow()

```

end if

Assume that it takes X amount of time to execute *computeLighting()* and Y amount of time to execute *computeShadow()* for a *batch* of sixteen pixels. In the situation where all sixteen pixels in a batch are all not in shadow, then it will take X amount for time to process the pixels. Alternatively, if all the pixels are shadowed it will take Y amount of time to process the pixels. In the unfortunate situation where some of the pixels are shadowed and some are not, X + Y amount of time must be spent to process the sixteen pixels.

As with any area of research it is often useful to examine how other researchers dealt with this issue in related fields. GPU architectures are sometimes referred to as *stream architectures*. Researchers have introduced the concept of conditional streams (Kapasi et al., 2000), which augment traditional streaming processors with the capability to conditionally read from input streams, and conditionally write to output streams.

#### 1.2.1 Conditional Streams

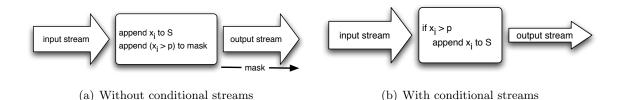

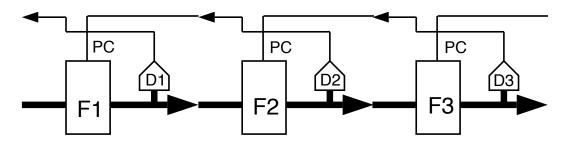

Figure 1.3(a) shows how a simple conditional operation would be handled by a streaming architecture without conditional streams. The goal of the compute kernel is to filter all the values that are below p. Since there must be a 1-to-1 correspondence between the input and output streams, all of the input values must be copied to the output. A mask is also generated to inform downstream kernels which elements of the output stream are valid. Since the mask can disable processing of some elements, the stream processors will not be fully utilized.

Figure 1.3(b) shows how the same conditional operation would be handled with conditional output streams. In this situation, the kernel can conditionally write values that are greater than p to the output stream. Since the output stream is only as large as it needs to be, the downstream kernels will fully utilize the stream processor since the output stream is densely packed.

Conditional output streams enable the efficient implementation of if-else style branches, and have the advantage that they can be implemented with a negligible performance penalty, only several additional gate delays. Conditional streams allow for a dramatic increase in processor utilization, hence an increase in processing efficiency, and memory access coherence, and thereby increase in performance. Algorithms such as sorting, boosted Haar cascades (Viola and Jones, 2001) which are useful for object detection, and particle system simulations, in additional to many others both graphics and non-graphics related, would execute more efficiently if the GPU supported conditional streams.

#### 1.2.2 Contributions

Conditional streams provide the opportunity to increase the rendering performance of graphics hardware by enabling the efficient implementation of high-quality rendering algorithms, and by making more generalized computations efficient. In this dissertation, I discuss augmenting the the architectures of graphics processors with conditional streams. A change of this type has been suggested by Popa (Popa, 2004) who proposed the use of conditional streams for compiling data-dependent control flows on SIMD GPUs. Additionally, while Direct3D 10 has introduced the concept of geometry shaders (Blythe, 2006), which also have a similar capability to generate compacted streams of data. Although there are no graphics chips capable of implementing this feature of geometry shaders efficiently at this time. Prior work has reported on using conditional streams in GPUs, it does not directly address the problem of ray tracing. In this dissertation, I will focus on the use of conditional output streams to accelerate a novel ray tracing algorithm. In particular, I describe a ray tracing algorithm that takes advantage of conditional streams that is able to reduce the required memory bandwidth by more than an order of magnitude when compared to previous work using GPUs for raytracing.

## 1.3 The Circuit Axis: Asynchronous Techniques for Improving the Efficiency and Performance of GPUs

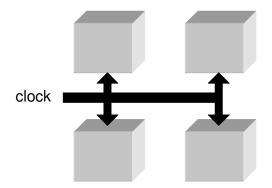

Current trends in micro-electronic design pose a challenge to synchronous systems: (i) high clock speed, (ii) large die area, (iii) handling worst-case delay in deep submicron processes (e.g. 90 nm and smaller), and (iv) managing large, complex designs. As a result, an alternative paradigm—*asynchronous* or "clockless" design—is becoming an increasingly attractive approach because of asynchronous logic's promise in reversing these negative trends (Berkel et al., 1999). As illustrated in Figure 1.4, instead of using global clocking, an asynchronous system uses *handshaking* between interacting components to achieve local synchronization.

Asynchronous design has potentially significant energy and performance benefits: lower energy consumption results due to elimination of the power wasted driving the clock, and by limiting switching activity to when and where needed (Berkel et al., 1999). Since local handshaking is used instead of a global clock for synchronization, asynchronous components can gain performance benefits by exploiting the data-dependency of computation completion times (Nowick et al., 1997; Rotem et al., 1999).

Since underlying circuit implementations can largely be decoupled from system level architecture, the circuit designer is basically free to use exotic techniques, such as clockless logic, while leaving the system architecture unchanged. For example, some modern CPUs, e.g. the Pentium 4, use asynchronous logic to implement their arithmetic units, while still

(a) A synchronous system, featuring centralized control

(b) An asynchronous system, with distributed control

Figure 1.4: Synchronous and asynchronous system block diagrams.

realizing a standardized architecture that appears unchanged at a high level. At the extreme, an entire micro-controller has been implemented with asynchronous circuits. This processor is a functional, drop-in replacement for standard synchronous micro-controller (Gageldonk et al., 1998).

#### 1.3.1 Contributions

The work presented in the dissertation involving what we have termed the *circuit axis* makes use of asynchronous logic, and increases rendering performance by making graphics hardware more energy efficient, while operating faster for the average case. The dissertation introduces two novel concepts: (i) the *compute-on-demand* paradigm, whereby computation at the bitlevel is on performed on an as-needed case, and (ii) a novel implementation of the counterflow pipeline architecture. In particular it extends the high capacity (HC) asynchronous pipelining style, which in turn uses dynamic logic, both of which will be briefly described below, and in more detail in Chapter 3.4.

Figure 1.5(a) shows a rendered image from the game Unreal Tournament 2004 (Epic Games, 2004), and Figure 1.5(b) shows a histogram of the number of bits that actually need to be compared per depth comparison to render the image. In Chapter 3, I will present a novel z-comparator that is both energy-efficient and fast. The comparator gains its increased performance by taking advantage of average case performance, and introduces my compute-on-demand paradigm.

Figure 1.5: Image (a) shows a frame from Unreal Tournament 2004. The frame requires 6,768,766 comparisons of incoming fragments with the depth buffer. On average, only the 7.3 most significant bits are actually needed to resolve each comparison. Figure (b) shows the distribution of z-comparison compute chain length for the frame shown in (a).

Additionally, I describe an asynchronous Booth multiplier that uses a novel implementation of a counterflow architecture (Sproull et al., 1994) in a single pipeline. In a counterflow architecture, data flows in one direction and control information flows in the opposite direction. This counterflow architecture allows for shorter critical paths, and therefore higher operating speed.

While using asynchronous logic in graphics hardware would require dramatic changes at the circuit-level, it would not require (or prevent), changes at the architectural or algorithmic levels.

### 1.4 Thesis Statement

Using multiple techniques at the circuit, architectural, and algorithmic levels, it is possible to increase the rendering performance of graphics hardware, where rendering performance can be defined as either increasing the energy efficiency of computation, increasing the speed of computation or increasing the visual quality of rendered images.

• Efficient construction of summed-area tables on commodity graphics hardware makes possible dynamic, real-time glossy environmental reflections and dynamic real-time image-based lighting without requiring changes to the underlying architecture.

- Conditional output streams facilitate an implementation of ray tracing that reduces memory-bandwidth, and allows for high-quality, geometrically correct reflection, refraction, and shadows.

- Asynchronous design techniques, increase energy efficiency, decrease area usage, and increase throughput of basic components used in graphics pipelines.

### **1.5** Major Contributions

This dissertation presents research at the circuit, architectural, and algorithmic levels that improves the energy efficiency of graphics processors, increases the speed of the computations, and increases the visual quality of rendered images.

My research contributions include along the three axes are:

- Algorithm Axis

- Efficient construction of summed-area tables: I describe a method using graphics hardware to rapidly generate summed-area tables that is efficient enough to allow multiple tables to be generated every frame while maintaining interactive frame rates. Several possible applications of using summed-area tables in interactive graphics are presented.

- Offset summed-area tables: I propose a technique that alleviates the precision requirements needed in the construction and use of summed-area tables by offsetting the input image by a constant value. This method improves precision in two ways: (i) there is a 1-bit gain in precision because the sign bit now becomes useful, and (ii) the summed-area function becomes non-monotonic, and therefore the maximum value reached has a relatively lower magnitude, thereby significantly increasing precision by lowering the dynamic range needed to store a summed-area table.

- Fast image-based lighting using summed-area tables: I present a method to rapidly generate higher-order summed-area tables — e.g., a summed-area table

of a summed-area table — that is efficient enough to allow multiple tables to be generated every frame while maintaining interactive frame rates. I demonstrate using higher order summed-area tables to approximate reflections generated using a Phong BRDF and high dynamic range environment maps.

#### • Architecture Axis

- Novel ray tracing algorithm using conditional streams: I propose a novel streaming ray casting algorithm. The algorithm uses conditional output streams to reduce memory bandwidth and increase processor utilization when compared to previous methods. The algorithm is able to reduce memory bandwidth by over an order of magnitude compared to the most efficient method presented so far. One possible use for our proposed technique is to implement hybrid rendering algorithms that use standard z-buffering techniques to generate the first hits from the camera view, and then use ray tracing to generate geometrically correct reflections and shadows.

#### • Circuit Axis

- Compute-on-demand paradigm for asynchronous circuits: I introduce the notion of compute-on-demand as a design principle for fast and energy-efficient graphics hardware. The key idea is to exploit the data-dependent nature of computation, and to obtain speed and energy improvements by optimizing the design for the common case, instead of assuming worst-case operation. An asynchronous or clockless circuit style is used to facilitate this paradigm. In particular, only those portions of compute blocks are activated that are actually required for a particular operation, thereby saving energy and reducing critical delays.

- Novel conterflow pipeline approach: I propose a novel implementation of counterflow pipelining which has significant advantages compared with previous implementations; it eliminates the need for complex synchronization and arbitration required between the two distinct data streams in the original counterflow implementation. This feature allows shorter critical paths, and therefore higher

operating speed. To demonstrate my counterflow methodology, I introduce a novel multiplier organization, in which the data bits flow in one direction, and the Booth commands are piggybacked on the acknowledgments flowing in the opposite direction.

## 1.6 Dissertation Organization

The remainder of this dissertation is organized as follows:

Chapter 2 discusses increasing rendering performance at the algorithmic level. First, I present background information on summed-area tables, pre-filtering environment maps, and image-based lighting is presented. Next, a method to rapidly construct summed-area tables using graphics hardware is described. Then, a technique to improve the precision requirements of summed-area tables, called offset summed-area tables is presented. Example applications are then described. Next, a method to construct higher-order summed-area tables in real-time is presented. Finally, a dynamic, real-time approximate image-based lighting algorithm.

Chapter 3 describes an architectural extension to commodity graphics processors that would improve processor utilization during execution o conditional operations. The chapter begins by presenting background information on conditional output streams, and GPU-based ray tracing algorithms. Next, as an example of the benefits of conditional streams, a novel ray tracing algorithm is presented. Then the performance of the algorithm is discussed.

Chapter 4 covers techniques used to improve graphics hardware efficiency and performance at the circuit level. It begins with an overview of asynchronous logic, with a particular emphasis on the High Capacity (HC) pipelining style. Next, a novel asynchronous z-comparator is presented which introduces and illustrates the compute-on-demand paradigm. Then two asynchronous Booth multipliers are presented to demonstrate the proposed counterflow pipelining style. Finally, an experiment designed to examine the relationship between pipeline complexity and average-case performance is discussed.

Chapter 5 concludes my dissertation with a summary of my contributions and discusses possible future work.

#### CHAPTER 2

# Increasing Rendering Performance Along the Algorithmic Axis

In this chapter, I present techniques that increase rendering quality on current commodity GPUs. In the next section background information will be presented along with related work. Next, my method for summed-area table construction will be discussed in detail. Additionally, a novel modification to standard summed-area tables, which I have term offset summed-area tables, will be presented. Finally multiple novel algorithms are presented which use summed-area tables to increase the quality of renderings. All of the algorithms presented in this chapter depend on the ability to rapidly generate multiple summed-area tables at interactive rates.

In (Kautz et al., 2000), Kautz et al. presented a method for real-time rendering of glossy reflections for static scenes. They rendered a dual-paraboloid environment map and prefiltered it in an offline process. Instead of pre-filtering, my algorithm creates a summed-area table for each face of a dual-paraboloid map on the fly, and uses them to filter the environment map at run time. This enables real-time, interactive environmental glossy reflections for dynamic scenes.

### 2.1 Background

In this section, I present background information on several techniques used as the basis for the research presented in this chapter, including environment mapping, summed-area tables, and high-dynamic range images. Then I discuss several related techniques that use mipmaps instead of summed-area tables to perform image filtering.

#### 2.1.1 Reflection and Environment Mapping

Reflection and environment mapping (Blinn and Newell, 1976) are a set of techniques that are useful for approximating reflection and refraction without having to resort to using ray tracing, which can be expensive or even impossible due to architectural limitations on current graphics hardware.

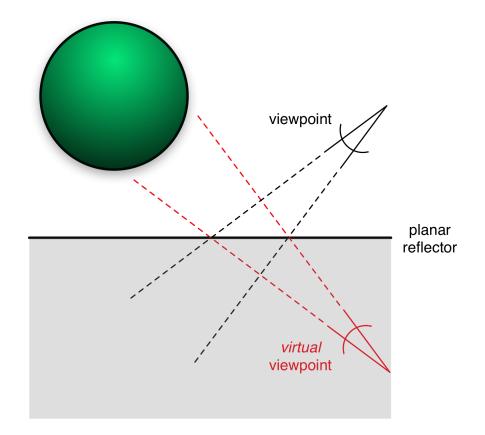

Figure 2.1: Planar reflection mapping. A virtual camera is placed opposite the planar reflector from the actual camera to generate planar reflections.

#### 2.1.1.1 Planar Reflection Mapping

Planar mirror reflections are generated by a relatively simple process whereby the scene is rendered from the view point of a virtual camera that is located on the opposite side of the planar reflector from the actual camera (Figure 2.1). On modern graphics hardware this procedure is accomplished using additional rendering passes, and rendering the results into a texture for use in the final rendering pass. This technique has the benefit of generating physically correct reflections, but suffers from performance issues when there are a large number of planar reflectors, since the scene must be re-rendered separately for each reflector.

#### 2.1.1.2 Cube Mapping

Environment mapping typically assumes that the reflective object, the reflector, is surrounded by a shell, such as a sphere (spherical mapping) or more commonly a cube (cube mapping), and then the environment is projected onto the surrounding shell using the center of the shell as the center of projection. For cube mapping, this process simply requires the scene to be rendered six times, once for each face of the cube. Then during the final rendering pass, the normal to the reflector and the view direction are used to compute a reflection direction which is used to lookup values from the *cubemap*. Modern graphics chips include support for automatically sampling the correct cube map face given a direction in 3-space.

Most environment mapping techniques make the simplifying assumption that the reflected environment is far from the reflector. When the reflector is relatively close to the environment, or if the center of the reflector is not near the center of the environment map, geometric distortions may be visible since the map has been generated with the center of an enclosing surface as the center of projection.

#### 2.1.1.3 Dual-Paraboloid Mapping

Dual-paraboloid environment mapping (Heidrich and Seidel, 1998) is a technique that stores an environment map in two textures, each of which stores half of the environment as reflected by a parabolic mirror (see Figure 2.2). Typically the alpha channel of each dual-paraboloid map face stores a circular mask that indicates whether a pixel contains relevant data.

A direct mapping from a cube map to a dual-paraboloid map is given by Blythe (Blythe, 1999). The following High Level Shader Language (HLSL) code performs the mapping for the front face of the dual-paraboloid map.

samplerCube tCube; // the cubemap to covert to a dual-paraboloid map

(a) Example dual-paraboloid map. The left column shows the *front* map, and the right column shows the *back* map.

(b) Diagram of a dual-paraboloid map projection. The reflected rays are parallel to each other.

| Figure 2.2: Dual-paraboloid m | laps. |

|-------------------------------|-------|

|-------------------------------|-------|

```

float 4 main (float2 inUV : TEXCOORDO /* quad texcoord from 0..1 */ )

: COLOR

{

float2 uv = 2.0 * inUV - 1.0; // scale and bias into -1..1 range

float3 dir; // lookup direction for cubemap

// convert front dual-paraboloid face texture coordinate to 3D

// direction

dir.x = 2.0*uv.x;

dir.y = 2.0*uv.y;

dir.z = -1.0 + dot( uv, uv );

dir /= (dot( uv, uv ) + 1.0);

// compute circular mask for alpha channel

float alpha = (dot( uv, uv ) < 1.0 ) ? 1.0 : 0.0;</pre>

```

```

// look up cubemap texture sample and multiply with alpha mask

return float4(texCUBE( texCUBE(tCube, dir).rgb, 1.0) * alpha;

```

A similar shader is used to compute the values for the back map. An alternative to converting 2D texture coordinates to a 3D direction vector in the shader is to pre-compute the conversion and store it in a lookup texture. Then at run-time, an indirect texture lookup is performed during generation of a dual-paraboloid map.

#### 2.1.2 High-Dynamic Range Images

}

Images in computer graphics are typically represented using low-dynamic range (LDR) values, since the archetypal display can display only a relatively limited dynamic range (the intensity range between black and white). Current commodity LCD displays typically only have a dynamic range on the order of 1000 to 1, whereas real world data will have a dynamic range several orders of magnitude larger.

Instead of using an integer value to represent the intensity of each color channel of an image, high-dynamic range (HDR) images typically use floating point values to represent the intensity of each channel, and allows for more realistic lighting and rendering effects. The availability of commodity graphics processors with single precision floating point native data paths, makes processing HDR data an attractive proposition that can dramatically increase the quality of rendered imagery. Given the limited capabilities of current display technologies, HDR data does have to be mapped to a LDR data via a process called *tone mapping*. Tone mapping is a separate topic from the material covered in this chapter, and will not be discussed further in this thesis.

#### 2.1.3 Image-Based Lighting

Image-based lighting (IBL), a technique introduced by Debevec (Debevec, 1998; Debevec, 2002), enables synthetic objects to be rendered into *real* scenes with realistic lighting. This dramatically increases the perceived realism of the synthetic objects. As presented by Debevec, IBL uses a *lightprobe*, which is simply an HDR environment map of real world data.

Lightprobes are typically captured from multiple images taken of a mirrored sphere, which allows radiance data to be captured in all directions. Once a lightprobe is generated, ray tracing is used to compute the incident illumination from the image-based lighting environment on each of the synthetic surfaces in the rendered scene (see Figure 2.3).

Figure 2.3: Image based lighting.

Assuming that normalized coordinates are used to access the lightprobe, directions in 3-space can be generated by rotating an normalized vector pointing in the direction of the -z-axis by  $\theta$  and  $\phi$ , where  $\theta$  and  $\phi$  are given by

$$u = [-1, 1], v = [-1, 1]$$

$$\theta = \arctan(v/u)$$

$$\phi = \pi * \sqrt{(u^2 + v^2)}$$

Using these relationships, it is a relatively simple task to generate HDR cube and dualparaboloid environment maps from real world data.

When a local-lighting model is used, an approximation of IBL is to simply convolve a

synthetic object's BRDF with a lightprobe, thereby approximating the lighting that the synthetic object would have received had it been located at the position where the lightprobe was taken. The use of ambient occlusion (Pharr, 2004) further increases the quality of this approximation.

# 2.2 Summed-Area Tables

As described in Section 1, summed-area tables enable the rapid calculation of the sum of the pixel values in an arbitrarily sized, axis-aligned rectangle at a fixed computational cost. Figure 1.1 illustrates how a summed-area table is used to compute the sum of the values of pixels spanning a rectangular region. To find the integral of the values in the dark rectangle, we begin with the pre-computed integral from (0,0) to  $(x_R, y_T)$ . We subtract the integrals of the rectangles (0, 0) to  $(x_R, y_B)$  and (0, 0) to  $(x_L, y_T)$ . The integral of the hatched box is then added to compensate for having been subtracted twice.

The average value of a group of pixels can be calculated by dividing the sum by the area. Crow's technique amounts to convolution of an input image with a box filter. The power lies in the fact that the filter support can be varied at a per pixel level without increasing the cost of the computation. Unfortunately, since the value of the sums (and thus the dynamic range) can get quite large, the table entries require extended precision. The number of bits of precision needed per component is

$$P_s = \log_2(w) + \log_2(h) + P_i$$

where w and h are the width and height of the input image.  $P_s$  is the precision required to hold values in the summed-area table, and  $P_i$  is the number of bits of precision of the input. Thus, a 256x256 texture with 8-bit components would require a summed-area table with 24 bits of storage per component.

Another limitation of Crow's summed-area table technique is that it is only capable of implementing a simple box filter. This is because only the sum of the input pixels is stored; therefore it is not possible to directly apply a more complex filter by weighting the inputs.

#### 2.2.1 Higher-Order Summed-Area Tables

In (Heckbert, 1986), Heckbert extended the theory of summed-area tables to handle more complex filter functions. Heckbert made two key observations. The first is that a summedarea table can be viewed as the integral of the input image, and the second that the sample function introduced by Crow was the same as the derivative of the box filter function. By taking advantage of those observations and the following convolution identity

$$f\otimes g=f'^n\otimes \int^n g$$

it is possible to extend summed-area tables to compute higher order filter functions, such as a Bartlett filter, or even a Catmull-Rom spline filter. The process is essentially one of repeated box filtering. Higher order filters approach a Gaussian, and exhibit fewer artifacts such as the blockiness associated with box-filtering.

For instance, Bartlett filtering requires taking the second-order box filter, and weighting it with the following coefficients:

Unfortunately, a direct implementation of the Bartlett filtering example requires 44 bits of precision per component, assuming 8-bits per component and a 256x256 input image.

In general, the precision requirements of Heckbert's method can be determined as follows:

$$P_s = n * (log_2(w) + log_2(h)) + P_i$$

where w and h are the width and height of the input texture, n is the degree of the filter function,  $P_i$  is the input image's precision, and  $P_s$  is the required precision of the  $n^{th}$ -degree summed-area table (Heckbert, 1986).

#### 2.2.2 Related Techniques

Various techniques (Ashikhmin and Ghosh, 2002; Yang and Pollefeys, 2003) have been presented that combine multiple samples from different levels of a mipmap to approximate filtering. Ashikhmin and Ghosh approximate simple blurry reflections by using multiple samples from a mipmapped environment map instead of pre-filtering the environment map (Ashikhmin and Ghosh, 2002). By using multiple samples, they are able to approximate various simple BRDFs and blur the environment map on the fly, giving objects the appearance of having glossy BRDFs. Yang and Pollefeys use the same approach to assist in performing depth correlation on a pair of stereo images. They take multiple samples from the mip-map and sum them together to approximate a smooth filter functions.

These techniques suffer from several problems. First, a small step in the neighborhood around a pixel does not necessarily introduce new data to the filter; it only changes the weights of the input values. Second, when the inputs do change, a large amount of data changes at the same time, due to the mipmap, which causes noticeable artifacts. Demers et al. (Demers, 2004) added noise in an attempt to make the artifacts less noticeable; although, the visual quality of the resulting images was noticeably reduced.

#### 2.2.3 Efficient Summed-Area Table Generation on GPUs

This section presents one of the major contributions of this thesis. In particular I present a technique to rapidly generate summed area tables on GPUs. In order to efficiently construct summed-area tables, I borrow a technique, called recursive doubling (Dubois and Rodrigue, 1977), often used in high-performance and parallel computing. Using recursive doubling, a parallel gather operation amongst n processors can be performed in only  $log_2(n)$  steps, where a single step consists of each processor passing its accumulated result to another processor.

In a similar manner, the method presented uses the GPU to accumulate results so that only  $O(\log n)$  passes are needed for summed-area table construction. To simplify the following description, I assume that only two texels, *texture elements*, can be read per pass. Later in the discussion I explain how to generalize the technique to an arbitrary number of texture reads per pass.

Figure 2.4: The recursive doubling algorithm in 1D. On the first pass, the value one element to the left is added to the current value. On the second pass, the value two elements to the left is added the current value. In general, the stride is doubled for each pass. The output is an array whose elements are the sum of all of the elements to the left, computed in  $O(\log n)$  time.

The algorithm proceeds in two phases: first a horizontal phase, then a vertical phase. During the horizontal phase, results are accumulated along scan lines, and during the vertical phase, results are accumulated along columns of pixels. The horizontal phase consists of n passes, where n = ceil(log2(image width)), and the vertical phase consists of m passes, where m = ceil(log2(image height)).

For each pass a screen-aligned quad is rendered that covers all pixels that do not yet hold their final sum. This prevents pixels that have already computed their final value from wasting precision resources. The input image is stored in a texture named  $t_A$ . In the first pass of the horizontal phase two texels are read from  $t_A$ : the one corresponding to the pixel currently being computed and the one to the immediate left. They are added together and stored into texture  $t_B$ .

For the second pass, the textures are swapped so that data is read from  $t_B$  and written to  $t_A$ . Now the fragment program adds the texels corresponding to the one currently being computed and the one two pixels to the left.  $t_A$  now holds the sum of four pixels.

The third pass repeats this scheme, now reading from  $t_A$  and writing to  $t_B$  and summing two texels four pixels apart, resulting in the sum of eight pixels in  $t_B$ . This progression continues for the rest of the horizontal passes until all pixels are summed up in the horizontal direction. Note that in pass *i* the leftmost  $2^i$  pixels already hold their final sum for the horizontal phase and thus are not covered by the quad rendered in this pass. Next the vertical phase proceeds in an analogous manner. Figure 2.4 shows the horizontal passes needed to construct a summed-area table of a 4x4 image. The following pseudo-code summarizes the algorithm.

$t_A \Leftarrow InputImage$   $n \Leftarrow log_2(width)$   $m \Leftarrow log_2(height)$ // horizontal phase  $i \Leftarrow 0$ for i < n do  $t_B[x, y] \Leftarrow t_A[x, y] + t_A[x + 2^i, y]$   $swap(t_A, t_B)$   $i \Leftarrow i + 1$ end for

// vertical phase

$$i \leftarrow 0$$

for  $i < m$  do

$t_B[x, y] \leftarrow t_A[x, y] + t_A[x, y + 2^i]$

$swap(t_A, t_B)$

$i \leftarrow i + 1$

end for

// Texture  $t_A$  holds the result

In practice, reading more than two texels per fragment, per pass is possible, and this reduces the number of passes required to generate a summed-area table by at least a factor of two. The current implementation supports reading 2, 4, 8, or 16 texels per fragment, per pass. This allows trading per-pass complexity with the number of rendering passes required. Adding 16 texels per pass enables us to generate a summed-area table from a 256x256 image in only four passes, two for the horizontal phase, and two for the vertical phase. As shown later, adjusting the per-pass complexity helps in optimizing summed-area generation speed for different input texture sizes. The following is the pseudo-code to generate a summed-area table when r reads per fragment are possible.

$t_A \Leftarrow InputImage$  $n \Leftarrow log_r(width)$  $m \Leftarrow log_r(height)$

// horizontal phase

$i \Leftarrow 0$

for i < n do

$$t_B[x, y] \Leftarrow t_A[x, y] +$$

$$t_A[x + 1 * r^i, y] +$$

$$t_A[x + 2 * r^i, y] +$$

$$\cdots +$$

$$t_A[x + r * r^i, y]$$

$$swap(t_A, t_B)$$

$$i \Leftarrow i + 1$$

end for

// vertical phase  $i \Leftarrow 0$ for i < n do  $t_B[x, y] \Leftarrow t_A[x, y] +$  $t_A[x, y + 1 * r^i] +$

$$\begin{aligned} t_A[x,y+2*r^i] + & \\ \cdots + & \\ t_A[x,y+r*r^i] \\ swap(t_A,t_B) \\ i & \Leftarrow i+1 \end{aligned}$$

end for

i

// Texture  $t_A$  holds the result

Note that near the left and bottom image borders the fragment program will fetch texels outside the image regions. To ensure correct summation of the image pixels, the texture units must be configured to use *clamp to border color* mode with the border color set to 0. This way texel fetches outside the image boundaries will not affect the sum. Alternatively, it is possible to render a single pixel black border around the input image and configure the texture units to use *clamp to edge* mode.

The algorithm presented has been implemented in both Direct3D and OpenGL, with similar results. Tables 2.1 and 2.2 summarize the Direct3D results. The OpenGL implementation uses a double buffered pbuffer to mitigate the cost of context switches. Instead of switching context between each pass, the implementation simply swaps the front and back buffers of the pbuffer. This allows us to efficiently *ping-pong* between two textures as results are accumulated. The Direct3D implementation simply uses two different render targets. If implemented at the driver level, similar to the way that automatic mip-map generation is done, the costs of the passes would be reduced even more.

#### 2.2.4Summed-Area Table Generation Performance

Table 2.1 shows the time required to generate summed-area tables of different sizes on a number of graphics cards using DirectX 9. For each card, and for each of the three input image sizes, we show the shortest time to generate a summed-area table along with the number of texels read per fragment per pass that gives the best result.

|                        | Summed-area table size |              |              |

|------------------------|------------------------|--------------|--------------|

|                        | $256 \times 256$       | 512x512      | 1024x1024    |

| Radeon                 |                        |              |              |

| $9800 \ {\rm XT^1}$    | 3.1  ms (8)            | 14.2  ms (4) | 70.1  ms (4) |

| Radeon                 |                        |              |              |

| X800XT $PE^1$          | 1.4  ms (8)            | 7.3  ms (4)  | 36.2  ms (4) |

| Geforce                |                        |              |              |

| $6800 \text{ Ultra}^2$ | 4.3  ms (8)            | 32.4  ms (4) | 95.3  ms (4) |

Table 2.1: Shortest time to generate summed-area tables of different sizes. The number of samples per pass are given in parentheses.  ${}^{1}24 - bit floats$   ${}^{2}32 - bit floats$

|              | Summed-area table size |                    |                      |

|--------------|------------------------|--------------------|----------------------|

| Samples/pass | $256 \times 256$       | 512x512            | 1024x1024            |

| 2            | $2.3 \mathrm{ms}$      | $9.9 \mathrm{ms}$  | $44.3 \mathrm{ms}$   |

| 4            | $1.8 \mathrm{ms}$      | $7.3 \mathrm{ms}$  | $36.2 \mathrm{\ ms}$ |

| 8            | $1.4 \mathrm{ms}$      | $9.9 \mathrm{ms}$  | $45.6 \mathrm{ms}$   |

| 16           | $2.7 \mathrm{ms}$      | $12.4 \mathrm{ms}$ | $53.3 \mathrm{\ ms}$ |

Table 2.2: Time to generate summed-area tables of different sizes using different number of samples per pass on a Radeon X800XT Platinum Edition graphics card.

Table 2.2 shows performance based on input size and the number of samples per pass for one of the cards used in the tests. Benchmark results show that finding a good balance between the number of rendering passes and the amount of work performed during each pass is important for the overall performance of summed-area table generation. The optimal tradeoff between the number of passes and per-pass cost is largely dependent on the overhead of switching render targets, which typically causes a pipeline flush, and the design of the texture cache on the target platform.

Computing summed-area tables directly on the graphics card is better than performing this computation on the CPU for a two primary reasons. First, the input data is already present in GPU memory. Transferring the data to the CPU for processing and then back again would put an unnecessary burden on the bus and can easily become a bottleneck because many graphics drivers are unable to reach full theoretical bandwidth utilization when reading back data from the GPU (GPUBench, 2004). Moreover, moving data back and forth between GPU and CPU would break GPU-CPU parallelism because each processor would end up waiting for new results from the other processor.

# 2.3 Offset Summed-Area Tables

A key challenge to the usefulness of the summed-area table approach is the loss of numerical precision, which can lead to significant noise in the resultant image. This section first discusses the source of such precision loss and then presents my approach to mitigate this problem (this technique is also described in (Hensley et al., 2005)). Example images are provided that demonstrate how the approach achieves significant reduction in noise: up to 31 dB improvement in signal-to-noise ratios.

#### 2.3.1 Source of Precision Loss

One source of precision loss could be the GPU's floating-point implementation: Current graphics hardware does not implement IEEE standard 754 floating point but, as shown by Hillesland (Hillesland and Lastra, 2004), current GPU implementations behave reasonably well, so this is not the primary source of numerical error.