## CACHE-BASED SIDE-CHANNEL ATTACKS IN MULTI-TENANT PUBLIC CLOUDS AND THEIR COUNTERMEASURES

Yinqian Zhang

A dissertation submitted to the faculty of the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

Chapel Hill 2014

Approved by: Michael K. Reiter Jan Prins Ari Juels Bryan Parno Thomas Ristenpart

©2014 Yinqian Zhang ALL RIGHTS RESERVED

## ABSTRACT

Yinqian Zhang: Cache-based Side-Channel Attacks in Multi-Tenant Public Clouds and Their Countermeasures (Under the direction of Michael Reiter)

Cloud computing is gaining traction due to the business agility, resource scalability and operational efficiency that it enables. However, the murkiness of the security assurances offered by public clouds to their tenants is one of the major impediments to enterprise and government adoption of cloud computing. This dissertation explores one of the major design flaws in modern public clouds, namely insufficient isolation among cloud tenants as evidenced by the cloud's inability to prevent side-channel attacks between co-located tenants, in both Infrastructure-as-a-Service (IaaS) clouds and Platform-as-a-Service (PaaS) clouds. Specifically, we demonstrate that one virtual machine (VM) can successfully exfiltrate cryptographic private keys from another VM co-located on the same physical machine using a cache-based side-channel attack, which calls into question the established belief that the security isolation provided by modern virtualization technologies remains adequate under the new threat model in multi-tenant public IaaS clouds. We have also demonstrated in commercial PaaS clouds that cache-based side channels can penetrate container-based isolation by extracting sensitive information from the execution paths of the victim applications, thereby subverting their security. Finally, we devise two defensive techniques for the IaaS setting, which can be adopted by cloud tenants immediately on modern cloud platforms without extra help from cloud providers, to address side-channel threats: (1) for tenants requiring a high degree of security and physical isolation, a tool to facilitate cloud auditing of such isolation; and (2) for tenants who use multi-tenant cloud services, an operating-system-level defense to defend against cache-based side-channel threats on their own.

To my parents, who raised me to be a man of integrity and determination, encourage and support me unconditionally to pursue my dreams.

To my beloved wife, Ying, my biggest fan, who believes in me under any circumstances, cheers on my trivial achievements, and always stands beside me in the face of difficulties.

To my son, who is on his way to this beautiful world as of this writing. He brings joy, and makes my life more purposeful.

## ACKNOWLEDGMENTS

I want to express my heartfelt gratitude to my advisor, Dr. Michael Reiter, for taking me under his wings, guiding me to mature professionally as a researcher, sharing with me his relentless optimism when facing research challenges, and offering me freedom and support in pursuing my own research interests. He has inspired me as a role model with his strong dedication and incredible enthusiasm in his work. He was the reason I chose to enter this graduate program as a graduate student; and he is the reason I choose an academic career after graduation. He is the best advisor I could ever imagine.

My special thanks go to my collaborators and mentors. I am very grateful to Dr. Ari Juels, who has collaborated with me since the start of my dissertation research, for sharing his knowledge and passion with me, inspiring me to pursue creativity, and being unconditionally supportive to my research. I also wish to thank Dr. Fabian Monrose, who offered me extensive advice and valuable feedback in my research and study. I want to thank Dr. Alina Oprea and Dr. Thomas Ristenpart, for their dedication to our collaborative research projects and the enthusiasm they have exemplified to me in pursuing outstanding academic achievements. I will be forever in debt to my mentor at Google Research, Dr. Úlfar Erlingsson, who provided me with different perspectives in research, broadened my horizon and offered me priceless career advice and support. I am also grateful to Dr. Jan Prins and Dr. Bryan Parno for their feedback and valuable suggestions that help improve my dissertation.

At last, I would like to acknowledge the financial support to my research from National Science Foundation (Award Number 0756998, 0910483, and 1330599), from the Science of Security Lablet at North Carolina State University, from RSA Laboratories and VMWare, and also from Google by awarding me the Google Ph.D. fellowship in security.

# TABLE OF CONTENTS

| LI | LIST OF TABLES    |        |            |                           |     |

|----|-------------------|--------|------------|---------------------------|-----|

| LI | LIST OF FIGURES x |        |            |                           |     |

| LI | ST OI             | F ABBR | EVIATIO    | NS                        | xiv |

| 1  | INTI              | RODUC  | TION       |                           | 1   |

|    | 1.1               | Cross- | VM Crypt   | ographic Side Channels    | 3   |

|    | 1.2               | Co-Res | sidency De | etection                  | 6   |

|    | 1.3               | OS-Le  | vel Side-C | hannel Mitigation         | 8   |

|    | 1.4               | Cross- | Tenant Sid | e Channels in PaaS        | 9   |

| 2  | BAC               | KGROU  | UND ANI    | PRIOR WORK                | 12  |

|    | 2.1               | Crypto | graphic Si | de Channels in CPU Caches | 12  |

|    |                   | 2.1.1  | Caches in  | n Modern Architectures    | 12  |

|    |                   | 2.1.2  | Taxonom    | y of Cache Side Channels  | 13  |

|    |                   |        | 2.1.2.1    | Time-Driven Attacks       | 14  |

|    |                   |        | 2.1.2.2    | Trace-Driven Attacks      | 14  |

|    |                   |        | 2.1.2.3    | Access-Driven Attacks     | 14  |

|    |                   | 2.1.3  | Prime-Pr   | obe Protocols             | 15  |

|    |                   |        | 2.1.3.1    | Data Cache Probing        | 15  |

|    |                   |        | 2.1.3.2    | Instruction Cache Probing | 16  |

|    |                   | 2.1.4  | Sources    | of Noise                  | 17  |

|    |                   |        | 2.1.4.1    | Hardware Noise            | 17  |

|    |                   |        | 2.1.4.2    | Software Noise            | 18  |

|   | 2.2 | Cloud  | Computing and Side-Channel Threats          | 19 |

|---|-----|--------|---------------------------------------------|----|

|   |     | 2.2.1  | Infrastructure-as-a-Service Clouds          | 19 |

|   |     | 2.2.2  | Platform-as-a-Service Clouds                | 20 |

|   |     |        | 2.2.2.1 PaaS Isolation Techniques           | 20 |

|   |     |        | 2.2.2.2 Side Channels in PaaS               | 21 |

|   | 2.3 | Counte | ermeasures to Side-Channel Attacks          | 22 |

|   |     | 2.3.1  | Hardware-Layer Approaches                   | 22 |

|   |     | 2.3.2  | Hypervisor-Layer Approaches                 | 23 |

|   |     | 2.3.3  | OS-Layer Approaches                         | 23 |

|   |     | 2.3.4  | Application-Level Approaches                | 23 |

| 3 | CRC | SS-VM  | CRYPTOGRAPHIC SIDE CHANNELS                 | 24 |

|   | 3.1 | Overvi | iew and Challenges                          | 24 |

|   | 3.2 | Cross- | VM Side Channels                            | 27 |

|   | 3.3 | Cache  | Pattern Classifier                          | 29 |

|   | 3.4 | Noise  | Reduction                                   | 31 |

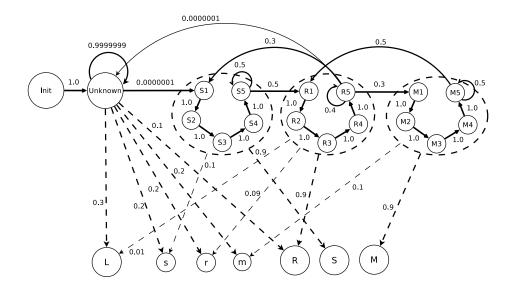

|   |     | 3.4.1  | Hidden Markov Model                         | 32 |

|   |     | 3.4.2  | Post-Processing HMM Outputs                 | 33 |

|   |     | 3.4.3  | Filtering out Non-Cryptographic HMM Outputs | 34 |

|   | 3.5 | Code-p | path reassembly                             | 35 |

|   |     | 3.5.1  | Cross-Fragment Error-Correction             | 36 |

|   |     | 3.5.2  | Fragment Stitching                          | 37 |

|   |     | 3.5.3  | Combining Spanning Sequences                | 38 |

|   | 3.6 | Evalua | tion                                        | 39 |

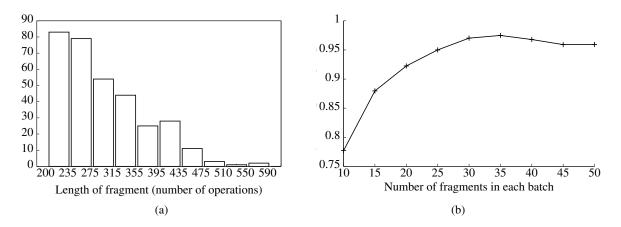

|   |     | 3.6.1  | With a Work-Conserving Scheduler            | 40 |

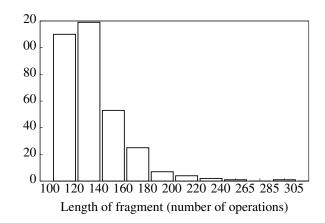

|   |     | 3.6.2  | With a Non-Work-Conserving Scheduler        | 42 |

|   | 3.7 | Discus | sion                                        | 43 |

|   |     | 3.7.1  | Applicability to Other Targets              | 43 |

|   |      | 3.7.2  | Countermeasures                               | 44 |

|---|------|--------|-----------------------------------------------|----|

|   | 3.8  | Summa  | ary                                           | 45 |

| 4 | CO-  | RESIDE | ENCY DETECTION                                | 47 |

|   | 4.1  | Motiva | tion and Threat Model                         | 47 |

|   |      | 4.1.1  | Threat Model                                  | 48 |

|   |      | 4.1.2  | Alternative Approaches                        | 50 |

|   | 4.2  | Design | ing a Co-Residency Detector                   | 50 |

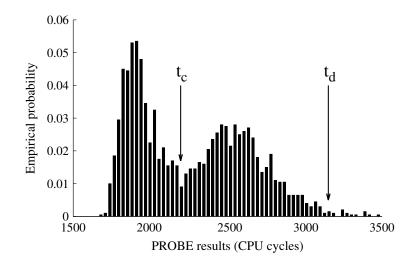

|   |      | 4.2.1  | A Single-Probe Classifier                     | 51 |

|   |      | 4.2.2  | A Multi-Probe Classifier                      | 53 |

|   |      | 4.2.3  | Training the Multi-Probe Classifier           | 57 |

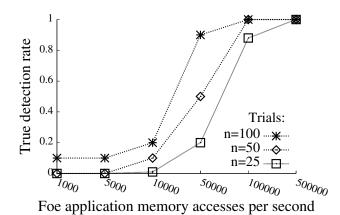

|   |      | 4.2.4  | Multi-Probe Detection Capability              | 58 |

|   | 4.3  | Implen | nentation                                     | 60 |

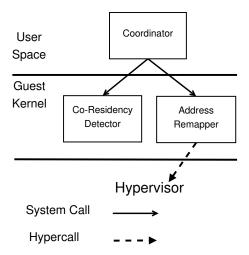

|   |      | 4.3.1  | Coordinator                                   | 60 |

|   |      | 4.3.2  | Address Remapper                              | 62 |

|   |      | 4.3.3  | Co-Residency Detector                         | 64 |

|   | 4.4  | Evalua | tion                                          | 65 |

|   |      | 4.4.1  | Detection                                     | 66 |

|   |      | 4.4.2  | Performance                                   | 70 |

|   | 4.5  | Discus | sion                                          | 72 |

|   | 4.6  | Summa  | ary                                           | 73 |

| 5 | OS-I | LEVEL  | SIDE CHANNEL MITIGATION                       | 75 |

|   | 5.1  | Design | Goals                                         | 75 |

|   | 5.2  | Cleans | ing Time-Shared Caches                        | 76 |

|   |      | 5.2.1  | Basic Design                                  | 76 |

|   |      | 5.2.2  | Optimizations                                 | 78 |

|   |      |        | 5.2.2.1 Limiting the Protection Scope         | 78 |

|   |      |        | 5.2.2.2 Skipping Unnecessary Cache Cleansings | 79 |

|   | 5.3 | Impler  | nentation   |                                          | 80  |

|---|-----|---------|-------------|------------------------------------------|-----|

|   | 5.4 | Evalua  | ation       |                                          | 82  |

|   |     | 5.4.1   | Security    | Evaluation                               | 82  |

|   |     |         | 5.4.1.1     | Attacking a "Dummy" Victim               | 83  |

|   |     |         | 5.4.1.2     | Case Study: Square and Multiply          | 86  |

|   |     | 5.4.2   | Performa    | ance Evaluation                          | 87  |

|   |     |         | 5.4.2.1     | Securing TLS Libraries                   | 88  |

|   |     |         | 5.4.2.2     | Securing Other Applications              | 90  |

|   |     |         | 5.4.2.3     | Sentinel/Battle Mode Switching           | 91  |

|   |     |         | 5.4.2.4     | Performance Overhead When Being Attacked | 92  |

|   | 5.5 | Discus  | ssion       |                                          | 92  |

|   |     | 5.5.1   | Extensio    | ns of Düppel                             | 92  |

|   |     | 5.5.2   | Limitatio   | Dns                                      | 93  |

|   | 5.6 | Summ    | ary         |                                          | 94  |

| 6 | CRC | OSS-TEI | NANT SIE    | DE CHANNELS IN PAAS CLOUDS               | 95  |

|   | 6.1 | Attack  | Framewo     | rk                                       | 95  |

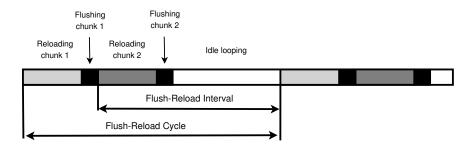

|   |     | 6.1.1   | Side Cha    | annels via Flush-Reload                  | 96  |

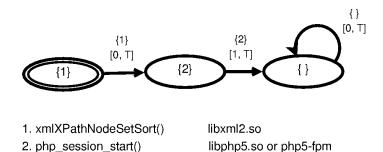

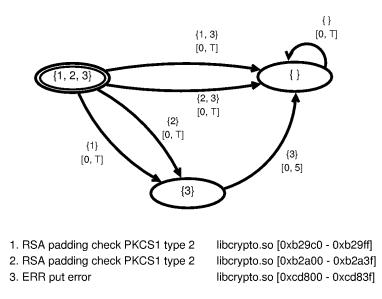

|   |     | 6.1.2   | From CF     | Gs to Attack NFAs                        | 98  |

|   |     | 6.1.3   | Applying    | g Attack NFAs                            | 100 |

|   | 6.2 | Co-Lo   | cation in F | PaaS                                     | 100 |

|   | 6.3 | Case S  | Study 1: In | ferring Sensitive User Data              | 104 |

|   |     | 6.3.1   | Attack B    | ackground                                | 104 |

|   |     | 6.3.2   | Evaluatio   | on in Public PaaS                        | 106 |

|   | 6.4 | Case S  | Study 2: Pa | assword-Reset Attacks                    | 107 |

|   |     | 6.4.1   | Backgro     | und on PRNG in PHP                       | 108 |

|   |     | 6.4.2   | Evaluatio   | on in Public PaaS                        | 110 |

|   | 6.5 | Case S  | Study 3: Bi | reaking SAML-based Single Sign-On        | 112 |

|    |      | 6.5.1  | Bleichenbacher Attacks    | 112 |

|----|------|--------|---------------------------|-----|

|    |      | 6.5.2  | Evaluation in Public PaaS | 113 |

|    | 6.6  | Discus | sion                      | 116 |

|    |      | 6.6.1  | Countermeasures           | 116 |

|    |      | 6.6.2  | Ethical Considerations    | 117 |

|    | 6.7  | Summ   | ary                       | 118 |

| 7  | CON  | NCLUSI | ON                        | 120 |

| BI | BLIO | GRAPH  | ΙΥ                        | 122 |

# LIST OF TABLES

| 2.1 | Example PaaS isolation techniques                            | 21  |

|-----|--------------------------------------------------------------|-----|

| 3.1 | Parameter settings in cross-VM attack evaluation             | 40  |

| 3.2 | Confusion matrix of SVM in cross-VM attack evaluation        | 41  |

| 5.1 | Confusion matrix of SVM classification without Düppel        | 87  |

| 5.2 | Confusion matrix of SVM classification with Düppel           | 87  |

| 6.1 | Number of sequentially launched instances before co-location | 103 |

| 6.2 | Experiment results of sensitive user data inferences         | 107 |

| 6.3 | Confusion matrix for padding error detection                 | 116 |

# LIST OF FIGURES

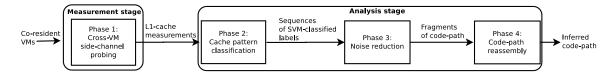

| 3.1 | Diagram of the main steps in the cross-VM side-channel attack             | 27  |

|-----|---------------------------------------------------------------------------|-----|

| 3.2 | The square-and-multiply algorithm of modular exponentiation               | 30  |

| 3.3 | Diagram of the Hidden Markov Model used in cross-VM attacks               | 33  |

| 3.4 | Experiment results with work-conserving scheduler                         | 42  |

| 3.5 | Experiment results with non-work-conserving scheduler                     | 43  |

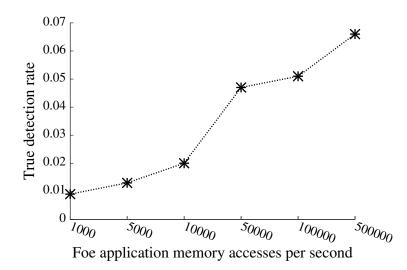

| 4.1 | True detection rate of the single-probe classifier                        | 52  |

| 4.2 | Distribution of timing results of PRIME-PROBE trials with no foe present  | 54  |

| 4.3 | True detection rate of the multi-probe classifier                         | 59  |

| 4.4 | Architecture of HomeAlone within one guest VM                             | 60  |

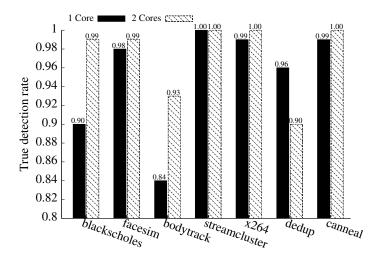

| 4.5 | True detection rates for different foe applications                       | 66  |

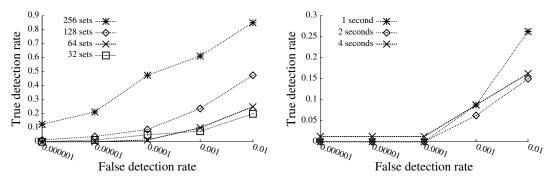

| 4.6 | ROC curve for detecting adversarial foe VMs with different aggressiveness | 68  |

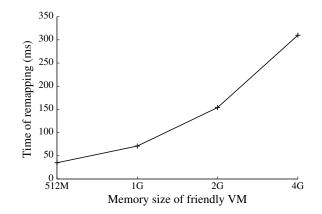

| 4.7 | Runtime of memory remapping as a function of memory size                  | 70  |

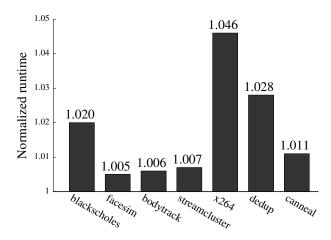

| 4.8 | Normalized performance of benchmark applications during detection periods | 71  |

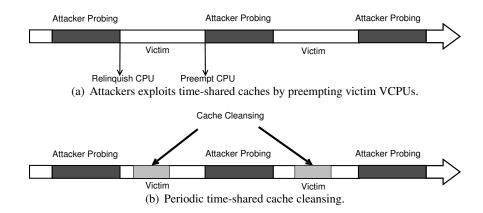

| 5.1 | Attack and defense on time-shared caches                                  | 77  |

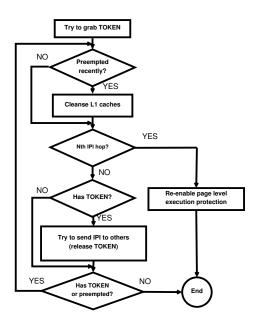

| 5.2 | A token-based IPI synchronization algorithm.                              | 82  |

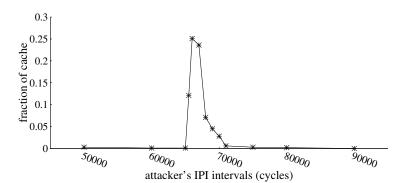

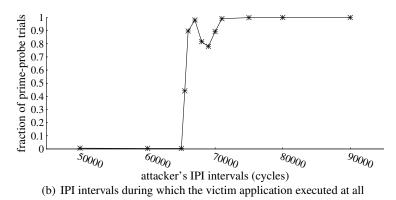

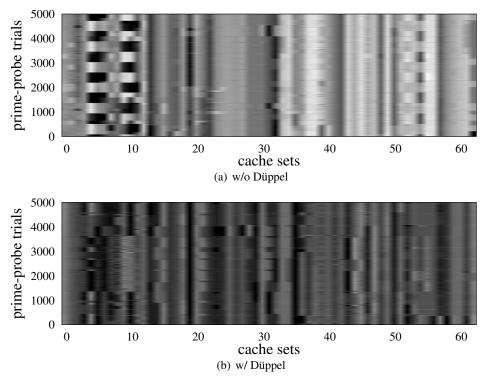

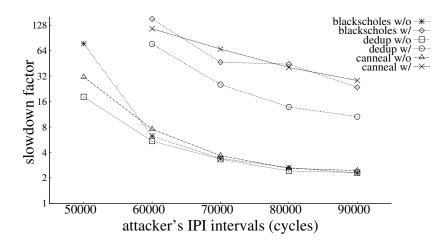

| 5.3 | Cache cleansing effectiveness under different attacker IPI intervals      | 84  |

| 5.4 | Attacker's view of L1 instruction cache timing                            | 85  |

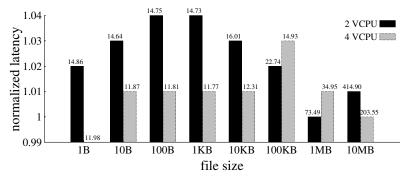

| 5.5 | Düppel's overheads for file download latency with different file sizes    | 88  |

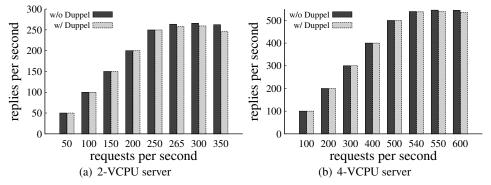

| 5.6 | Düppels overheads for file download rate in replies per second            | 89  |

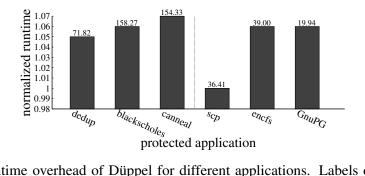

| 5.7 | Runtime overhead of Düppel for different applications                     | 90  |

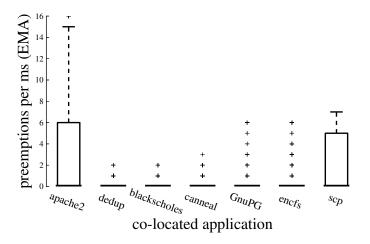

| 5.8 | Victim VCPU preemptions per ms induced by co-located application          | 92  |

| 5.9 | Performance overhead when under PRIME-PROBE attacks                       | 93  |

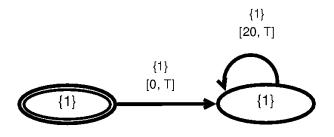

| 6.1 | An example of a FLUSH-RELOAD protocol                                     | 97  |

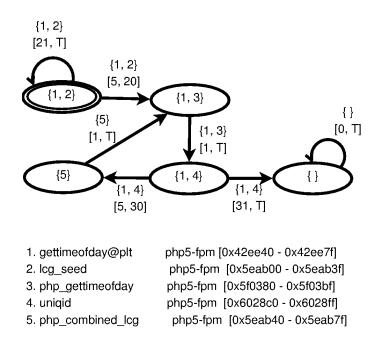

| 6.2 | The attack NFA used for detection of PaaS application co-location         | 102 |

| 6.3 | The attack NFA for inferring sensitive user data                      | 107 |

|-----|-----------------------------------------------------------------------|-----|

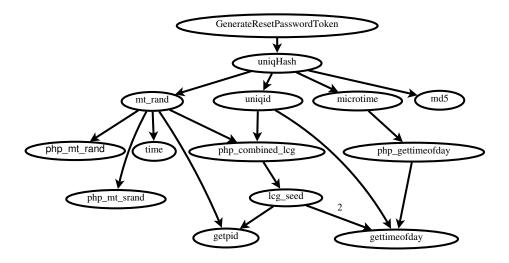

| 6.4 | The call graph of password reset token generation in PHP applications | 109 |

| 6.5 | The attack NFA for password-reset attacks                             | 111 |

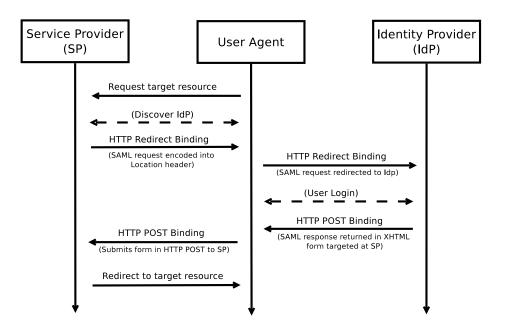

| 6.6 | The SAML 2.0 protocol evaluated in the single sign-on attacks         | 114 |

| 6.7 | The attack NFA for breaking SAML-based single sign-on                 | 116 |

# LIST OF ABBREVIATIONS

| ACPI   | Advanced Configuration and Power Interface   |

|--------|----------------------------------------------|

| APIC   | Advanced Programmable Interrupt Controller   |

| ASLR   | Address Space Layout Randomization           |

| BTB    | Branch Target Buffers                        |

| CFG    | Control-Flow Graph                           |

| CSR    | Cross-Site Request                           |

| DAC    | Discretionary Access Control                 |

| DP     | Dynamic Programming                          |

| EC2    | Elastic Compute Cloud                        |

| EMA    | Exponential Moving Average                   |

| GnuPG  | Gnu Privacy Guard                            |

| HMM    | Hidden Markov Model                          |

| HPET   | High Precision Event Timer                   |

| HVM    | Hardware-assisted Virtual Machine            |

| IaaS   | Infrastructure-as-a-Service                  |

| IDS    | Intrusion Detection System                   |

| IPI    | Inter-Processor Interrupt                    |

| NFA    | Nondeterministic Finite Automaton            |

| OS     | Operating System                             |

| PaaS   | Platform-as-a-Service                        |

| PCIDSS | Payment Card Industry Data Security Standard |

| PIT    | Programmable Interval Timer                  |

| PLT    | Procedure Linkage Table                      |

| PMU    | Performance Monitoring Unit                  |

| PRNG   | Pseudorandom Number Generator                |

| RCU    | Read-Copy-Update                             |

| SaaS   | Software-as-a-Service                        |

| SLA    | Service-Level Agreement                      |

| SMP  | Symmetric Multi-Processing      |

|------|---------------------------------|

| SMT  | Simultaneous Multi-Threading    |

| SVM  | Support Vector Machine          |

| TLB  | Translation Lookaside Buffer    |

| TLS  | Transport Layer Security        |

| TOFU | Trust on First Use              |

| TSC  | Time Stamp Counter              |

| VCPU | Virtual Central Processing Unit |

| VDI  | Virtual Desktop Infrastructure  |

| VM   | Virtual Machine                 |

## **CHAPTER 1: INTRODUCTION**

With its massive pooling and multiplexing of computing resources, the cloud offers enterprises the prospect of lower IT costs, lighter administrative burdens, and rapid scaling of resources. Based on the abstraction layer the cloud services export, they are commonly taxonomized as Software as a Service (SaaS), Platform as a Service (PaaS), or Infrastructure as a Service (IaaS). SaaS presents an application-level interface to the tenants, the customers of the cloud. PaaS offers an applicationdevelopment environment but abstracts away lower software layers such as the operating systems (OS) and programming language runtime environments. In an IaaS system, computing resources are generally made available to tenants in the form of virtual machine instances. Cloud services can also be categorized as public or private. Public clouds are operated for the benefit of multiple, organizationally distinct tenants—i.e., are multi-tenant environments—and generally available as dynamically provisioned, self-service offerings. Private clouds are operated for the benefit of a single tenant, often within a facility owned and managed by the tenant itself.

Security in a public cloud is a one of the major impediments to enterprise and government adoption of multi-tenant offerings (TrendMicro, 2011; NIST, 2012; Yeboah-Boateng and Essandoh, 2014; Shriver, 2014). By relinquishing control over their IT resources, cloud tenants expose themselves to less understood security models. They have little visibility into the design and implementation of the cloud security mechanisms, leaving them no choice but to rely on the security guarantees (usually not expressed explicitly) provided by the cloud vendors. The effectiveness of traditional security tools such as firewalls and intrusion detection systems (IDSs) diminishes in the cloud due to the obscure security perimeters. Even worse, new threats emerge in cloud computing. Because of the nature of multi-tenancy in public clouds, it has been widely perceived that businesses may find themselves sharing adjacent or overlapping computing resources with partners, suppliers, competitors, or attackers. The potential security threats from a co-located tenant have been projected but largely ignored in practice because of the blind faith in the cloud providers' ability to enforce strong isolation among different tenants.

This dissertation aims at exploring one of the major design flaws in public clouds—insufficient isolation between cloud tenants as evidenced by the inability to prevent side-channel attacks between them. Side channels exploited in our studies are primarily timing channels in the CPU caches, which allow secret information to be leaked across the boundary between cloud tenants. This insufficient isolation, we hypothesize, exists in both public IaaS and PaaS clouds.

In public IaaS clouds, e.g., Amazon's Elastic Compute Cloud (EC2) and Rackspace, tenants essentially have complete ownership of their VMs but no control over the lower layers of the infrastructure, i.e., hypervisors (a.k.a. virtual machine monitors or VMMs) and the cloud management fabric. The security isolation among VMs run by different tenants on the same physical server is provided by its virtualization technology (e.g., Xen) and its VMM. A VMM is designed to enforce strong logical isolation between the VMs so that one VM cannot access data possessed by another. However, analogous to the threat of cross-process side-channel attacks—e.g., low-privilege processes exfiltrating sensitive information from high-privilege processes via cache-based timing-channel analysis—cross-VM side-channel attacks have been a type of oft-discussed yet never demonstrated threat. The use of cache-based side channels to exfiltrate sensitive information, e.g., cryptographic keys, in virtualized environments, if successful, would significantly undermine the established belief that the security isolation provided by modern virtualization technologies remains adequate under the new threat model of multi-tenant public clouds.

Compared to IaaS clouds, PaaS provides different cloud service abstractions. With a PaaS user interface, the tenants are usually only allowed to upload the source code of their applications and launch the applications through the user control panels, without privileged accesses to the underlying, shared OS resources. As of today, many PaaS providers (e.g., Heroku, AppFog, DotCloud, Openshift) build their business on top of third-party IaaS clouds, and therefore are motivated economically to multiplex each VM to multiple (usually hundreds of) PaaS tenants. The high density of tenancy exacerbates the risks of insufficient tenant isolation in such environments. Existing side-channel attacks mountable by one process on another running in the same OS seem well suited to performing cross-tenant attacks in PaaS deployments. However, to the best of our knowledge, no such attack has been successfully demonstrated in PaaS settings, because the particular types of applications in PaaS,

which involves few cryptographic operations, are less susceptible to the existing side-channel attacks particularly designed to steal cryptographic keys. A novel approach that generalizes the cryptographic side channels to extract other sensitive information from PaaS-based applications and a successful demonstration of such attacks against realistic applications in public PaaS would provide strong evidence of the hypothesized, insufficient isolation, and call into question the dominant practices for isolating tenants in PaaS clouds.

This dissertation includes three major components. First of all, we demonstrate a cache-based cross-VM side-channel attack that extracts a cryptographic private key from another VM co-located on the same physical machine (outlined in Section 1.1 and detailed in Chapter 3). Such attacks evidence the insufficient isolation between IaaS cloud tenants in the face of hardware side channels, and call into question the use of multi-tenant clouds for security critical applications. Second, we propose two defensive techniques to address threats of such side-channel attacks in IaaS clouds. One defense, called HomeAlone, helps cloud tenants who request dedicated cloud servers to remotely verify that the tenant's VMs are physically isolated, even without help from the cloud provider (outlined in Section 1.2 and detailed in Chapter 4). Another defensive tool, named Düppel, allows tenants running on shared hardware to confound cache-based side-channel observations by modifying their VM's own OS kernels (see Section 1.3 and Chapter 5). Finally, we propose a general framework to apply cache-based side-channel attacks to PaaS-based applications, and demonstrate three practical attacks in public PaaS offerings (see Section 1.4 and Chapter 6).

Together, these results establish: *The design of, and common practices in, modern public multi-tenant IaaS and PaaS clouds are flawed in their insufficient isolation of cloud tenants from side-channel attacks by co-located tenants. However, in IaaS clouds, tenants can defend against prominent side-channel attacks by themselves with modified operating system kernels.*

## 1.1 Cross-VM Cryptographic Side Channels

Modern virtualization technologies such as Xen, KVM, HyperV, and VMWare are rapidly becoming the cornerstone for the security of many computing systems, including but not limited to IaaS public clouds. This reliance stems from their seemingly strong isolation guarantees, meaning their ability to prevent guest virtual machines running on the same system from interfering with each other's execution or, worse, exfiltrating confidential data across VM boundaries. The assumption of strong isolation underlies the security of public cloud computing systems (Ristenpart et al., 2009; Armbrust et al., 2010) such as Amazon EC2, Microsoft Windows Azure, and Rackspace; military multi-level security environments (Meushaw and Simard, 2000); home user and enterprise desktop security in the face of compromise (England and Manferdelli, 2006); and software-based trusted computing (Garfinkel et al., 2003).

VMMs of modern virtualization systems attempt to realize this assumption by enforcing logical isolation between VMs using traditional access-control mechanisms. But such logical isolation may not be sufficient if attackers can circumvent them via side-channel attacks. Concern regarding the existence of such attacks in the VM setting stems from two facts. First, in non-virtualized, cross-process isolation contexts, researchers have demonstrated a wide variety of side-channel attacks that can extract sensitive data such as cryptographic keys on single-core architectures (Percival, 2005; Osvik et al., 2006; Neve and Seifert, 2007; Aciiçmez and Seifert, 2007; Aciiçmez et al., 2007c,b; Aciiçmez, 2007; Tromer et al., 2010; Gullasch et al., 2011; Aciiçmez et al., 2010; Yarom and Falkner, 2013). The most effective attacks tend to be access-driven attacks (see Section 2.1) that exploit shared micro-architectural components such as caches. Second, Ristenpart et al. (2009) exhibited coarser, cross-VM, access-driven side-channel attacks on modern symmetric multi-processing (SMP, also called multi-core) architectures. But their attack could only provide crude information (such as aggregate cache usage of a guest VM) and, in particular, is insufficient for extracting cryptographic secrets.

Despite the clear potential for attacks, no actual demonstrations of fine-grained cross-VM sidechannels attacks have appeared. The oft-discussed challenges (Weiß et al., 2012; Ristenpart et al., 2009) to doing so stem primarily from the facts that VMMs place more layers of isolation between attacker and victim than in cross-process settings, and that modern SMP architectures do not appear to admit fine-grained side-channel attacks (even in non-virtualized settings) because the attacker and victim are often assigned to disparate cores. A lack of demonstrated attack is not a proof of security, and so whether fine-grained cross-VM side-channel attacks are possible has remained an important open question.

In Chapter 3, we will present the development and application of a cross-VM side-channel attack in exactly such an environment. Like many attacks before, ours is an access-driven attack in which the attacker VM alternates execution with the victim VM and leverages processor caches to observe behavior of the victim. However, we believe many of the techniques we employ to accomplish this effectively and with high fidelity in a virtualized SMP environment are novel. In particular, we provide an account of how to overcome three classes of significant challenges in this environment: (i) inducing regular and frequent attacker-VM execution despite the coarse scheduling quanta used by VMM schedulers; (ii) overcoming sources of noise in the information available via the cache timing channel, both due to hardware features (e.g., CPU power saving) and due to software ones (e.g., VMM execution); and (iii) dealing with core migrations, which give rise to cache "readings" with no information of interest to the attacker (i.e., the victim was migrated to a core not shared by the attacker). Finally, we customize our attack to the task of extracting a private decryption key from the victim and specifically show how to "stitch together" these intermittent, partial observations of the victim VM activity to assemble an entire private key.

As we demonstrate in a lab testbed, our attack establishes a side-channel of sufficient fidelity that an attacker VM can extract a private ElGamal decryption key from a co-resident victim VM running GNU Privacy Guard (GnuPG, http://www.gnupg.org), a popular software package that implements the OpenPGP e-mail encryption standard (Callas et al., 1998). The underlying vulnerable code actually lies in the most recent version of the libgcrypt library, which is used by other applications and deployed widely. Specifically, we show that the attacker VM's monitoring of a victim's repeated exponentiations over the course of a few hours provides it enough information to reconstruct the victim's 457-bit private exponent accompanying a 4096-bit modulus with very high accuracy—so high that the attacker was then left to search fewer than 10,000 possible exponents to find the right one.

We stress, moreover, that much about our attack generalizes beyond ElGamal decryption (or, more generally, discovering private exponents used in modular exponentiations) in libgcrypt. In particular, our techniques for preempting the victim frequently for observation and sidestepping several sources of cache noise are independent of the use to which the side-channel is put. Even those components that we necessarily tune toward ElGamal private-key extraction, and the pipeline of components overall, should provide a roadmap for constructing side-channels for other ends. We thus believe that our work serves as a cautionary note for those who rely on virtualization for guarding

highly sensitive secrets of many types, as well as motivation for the research community to endeavor to improve the isolation properties that modern VMMs provide to a range of applications.

## 1.2 Co-Residency Detection

Strong security isolation among tenants is a pillar of secure cloud computing. Logical isolation of computing resources can help protect against poorly or inadequately implemented or conceived access-control policies. However, virtual machines that execute on the same physical machine share a range of hardware resources—computing, memory, and so forth. Even when solid logical isolation ensures against abuse of explicit logical channels, shared hardware creates vulnerabilities to side-channel attacks. Due to the projection of such security risks, as evidenced by Ristenpart et al. (2009) and our research (described in Chapter 3), government agencies and enterprises often demand *physical* isolation for their cloud deployments. For example, NASA and Amazon negotiated a cloud service contract for seven months, due to wrangling over NASA's rights to hardware inspection (Stone and Vance, 2010). More recently, cloud providers started to provide isolated VM instances to customers with high security demands (e.g., Amazon introduced a new cloud service with physically isolated, tenant-specific hardware.)

While cloud providers may promise physical isolation, and even commit to it in service-level agreements (SLAs), enforcement by tenants and cloud auditors is a challenge. Cloud systems make heavy use of virtualization to abstract away underlying hardware for simplicity and flexibility. They are architected to be hardware opaque, not hardware transparent, and thus sit at odds with the goal of verifying physical isolation.

In Chapter 4, we will introduce *HomeAlone*, a new tool that allows a tenant or auditor to remotely verify that the tenant's VMs are physically isolated, i.e., that the tenant has exclusive use of a given physical machine. HomeAlone permits such verification with *no hypervisor modification*, and with no explicit action on the part of the cloud provider. The provider need not even be aware that HomeAlone is in operation. The key insight behind HomeAlone is that side channels aren't just vulnerabilities: They can aid *defensive* detection. HomeAlone exploits side channels (via the last-level cache) to detect undesired co-residency. The basic idea in HomeAlone is for the tenant to coordinate its VMs (called *friendly VMs*) so that they silence their activity in a selected cache

region for a period of time. The tenant then measures the cache usage during the resulting quiescent period and checks that there is no unexpected activity. Any such activity suggests the presence of a *foe VM*—our generic term for another tenant's VM—running on the same physical machine.

In practice, HomeAlone requires an approach more complicated than simple silencing of friendly VMs and listening for foe cache activity. Even without friendly VM activity, the last-level cache in a virtualized environment is never entirely quiet, and measurement of its activity (via techniques described in Chapter 2) is error-prone. The timing channel by which HomeAlone measures cache activity is subject to many forms of noise, including scheduling interruptions, coarse timer readings, and core migration in a multi-core environment. Even more challenging is the background noise created by low-level system activity (e.g., that of the hypervisor and Dom0 in Xen), which HomeAlone needs to distinguish from foe VM activity. Consequently, a major challenge in the design of HomeAlone is the construction of an effective classifier that can distinguish normal cache activity in a friendly environment from the activity introduced by a foe. This classifier in HomeAlone is carefully designed to address complications such as core migration and the impact of friendly-VM and Dom0 activity on the cache.

Another major technical challenge in HomeAlone is performance overhead: It is desirable in practice that silencing friendly VMs doesn't substantially degrade their performance. HomeAlone thus silences VMs in a *selective* manner. During detection periods, friendly VMs coordinate avoidance of just a small, randomly selected region of the cache, set aside for foe detection. Selective cache avoidance is challenging, and requires kernel modifications in the guest OS of the friendly VMs. By taking advantage of the double indirection layer in memory virtualization, we build an *address remapper* that remaps a set of physical memory pages (corresponding to the cache region avoided by friendly VMs) to a reserved pool of available pages. We show that the impact of selective cache avoidance on the performance of several realistic workloads is modest. For this reason, and because HomeAlone requires no hypervisor modification or cloud-provider support, tenants can use HomeAlone undisruptively and as often as desired to verify isolation policies.

We demonstrate that HomeAlone effectively detects foe VMs whose activities are significantly evidenced in the last-level cache during their execution. We believe that HomeAlone will most commonly detect policy misconfigurations or cost cutting by a service provider that produces undesired co-residency. We further show, however, that HomeAlone can impose significant obstacles even to hostile foe VMs that attempt to use the last-level cache as an avenue for side-channel attacks.

## 1.3 OS-Level Side-Channel Mitigation

In side-channel attacks in multi-tenant public clouds as demonstrated to date, shared CPU caches enable virtual machines administered by competing organizations to exfiltrate sensitive information from each other, which has been shown possible despite considerable interference and background "noise" from the hypervisor and other activities on the machine (see Chapter 3). A potential but very *expensive* solution, as discussed in Section 1.2, is to physically isolate mutually untrusted cloud tenants with high security demands, which may not be a viable solution for regular public cloud users who will continue the use of multi-tenant machines in public IaaS clouds.

Most approaches to address side-channel attacks in multi-tenant clouds have focused on altering the cloud platform in some way (see Section 2.3). However, to our knowledge, these defenses have not gained traction in existing public clouds. Rather, a typical tenant of a public cloud concerned about these attacks is left with little choice but to try to *defend itself*. One approach is to construct its software to resist side channels, e.g., (Molnar et al., 2006; Könighofer, 2008; Coppens et al., 2009), but these techniques can result in significant slowdown.

In Chapter 5 we will explore another possibility, namely a method by which a tenant can construct its VMs to automatically inject additional noise into the timings that an attacker might observe from caches. Since these timings are the most common side channels by which an attacker infers sensitive information about a victim VM, injecting noise into them will generally make the attacker's job more difficult. Our implementation of this idea, called Düppel<sup>1</sup>, modifies only the guest OS kernel and is general enough to protect arbitrary types of user-space applications. Düppel can be configured to protect the user-space application, any dynamically linked libraries it uses, or both. Düppel does not need support from hypervisors or cloud providers. To our knowledge, our scheme is the first work that provides tenant VM OS-layer mitigation of cross-VM side channels.

Unlike the noise overcome by previous attacks, the noise injected by Düppel is designed specifically to confound attacks mounted via timing the per-core L1 cache (or per-core L2 cache,

<sup>&</sup>lt;sup>1</sup>Düppel takes its name from a radar countermeasure developed by the German Luftwaffe during World War II, in which aircraft disperse clouds of tiny pieces of material to interfere with radar.

if present) on the platform. Düppel does so by repeatedly cleaning the L1 cache alongside the execution of its tenant workload, at a pace that it adjusts based upon the possibility with which timings reflecting the workload execution could actually have been observed from another VM. We also discuss extensions of Düppel to defeat timing attacks via other time-shared resources such as the branch prediction cache, should attacks via this cache (Aciiçmez et al., 2007c,b; Hund et al., 2013) someday be adapted to a virtualized setting. We emphasize, however, that even with just addressing the L1 cache, Düppel already interferes with all known cryptographic side-channel attacks that have been demonstrated in a virtualized SMP environment. (See Section 5.5 for further discussion on this point.)

Overhead of Düppel is modest. In tests on Amazon EC2, we show that file download latencies and server throughput over a TLS-protected connection from an Apache web server suffer by at most 4% when Düppel is configured to protect the OpenSSL library. We also demonstrate using the PARSEC benchmarks and other programs that computational workloads suffer by up to 7% when the applications are protected by Düppel. We believe that these overheads are acceptable given the substantial challenge involved in defending against cache-based side-channels with no help from the underlying hardware or hypervisor.

## 1.4 Cross-Tenant Side Channels in PaaS

Public PaaS clouds are an important segment of the cloud market, being projected for compound annual growth of almost 30% through 2017 (Mahowald et al., 2013) and "on track to emerge as the key enabling technology for innovation inside and outside enterprise IT" (Natis, 2014). For our purposes here, a PaaS cloud permits tenants to deploy tasks in the form of interpreted source (e.g., PHP, Ruby, Node.js, Java) or application executables that are then executed in a provider-managed host OS shared with other customers' applications. As such, a PaaS cloud often leverages OS-based techniques such as Linux containers to isolate tenants, in contrast to hypervisor-based techniques common in IaaS clouds.

A continuing threat to cloud tenant security is failures of isolation due to side-channel information leakage. A small but growing handful of works have explored side channels in settings characteristic of IaaS clouds, to which tenants deploy tasks in the form of virtual machines. Demonstrated attacks include side channels by which an attacker VM can extract coarse load measurements of a victim VM with which it is co-located (Ristenpart et al., 2009); identify pages it shares with a co-located victim VM, allowing it to detect victim VM applications, downloaded files (Suzaki et al., 2011) and its operating system (Owens and Wang, 2011); and even exfiltrate a victim VM's private decryption key (Chapter 3). However, only the first of these attacks was demonstrated on a public cloud, with the others being demonstrated only in lab settings. To the best of our knowledge, no side-channel attack capable of extracting granular information from a victim has been demonstrated in the wild.

In Chapter 6, we will initiate the study of cross-tenant side-channel attacks specifically in PaaS clouds and, in doing so, provide the first demonstration of granular, cross-tenant side channels in commercial clouds of any sort. Existing side-channel attacks mountable by one process on another running on the same OS, particularly those that leverage processor caches, e.g., (Percival, 2005; Neve and Seifert, 2007; Tromer et al., 2010; Gullasch et al., 2011; Yarom and Falkner, 2013), seem well suited to performing cross-instance<sup>2</sup> attacks in PaaS deployments. This is largely true in our experience, though directly leveraging these attacks in PaaS settings is not as straightforward as one might think. One reason is that even identifying suitable targets to attack in a PaaS deployment requires some thought. After all, cryptographic keys that commonly form their most natural targets are largely absent in typical PaaS environments where cryptographic protections (e.g., storage encryption, or application of TLS encryption to network traffic) are commonly provided as a service by the cloud operator, often on a different computer than those used to host tenant instances.

In Chapter 6, we will report on our investigation of cache-based side channels in PaaS clouds that, among other things, therefore identifies several novel targets (in the context of cross-tenant side-channel attacks) for PaaS environments: (i) We show how an attacker instance can infer aspects of a victim web application's responses to clients' service requests. In particular, we show that an attacker can reliably determine the number of distinct items in an authenticated user's shopping cart on an e-commerce site (the victim instance) running the popular Magento e-commerce application. (ii) We show how an attacker instance can hijack a user account on a web site (the victim instance) by predicting the pseudorandom number it embeds in a password reset link. We specifically demonstrate

<sup>&</sup>lt;sup>2</sup>While "instance" typically refers to an instantiated VM in an IaaS setting, here we borrow the term for the PaaS setting, to refer more generically to a collection of running computations on one physical machine that are associated with the same tenant and should be isolated from other tenants.

this attack against the PHP pseudorandom number generator that the site uses. (iii) We show how an attacker instance can monitor the victim so as to obtain a padding oracle to break XML encryption schemes. In particular, we demonstrate a Bleichenbacher attack (Bleichenbacher, 1998) against SimpleSAMLphp, an open-source SAML-based authentication application that implements PKCS#1 v1.5 RSA encryption in a manner resistant to these attacks via other vectors (but not via our side-channel attacks).

We stress, moreover, that we have successfully mounted each of these attacks in commercial PaaS clouds (though obviously against victims that we deployed ourselves). Moreover, as a side effect of doing so, we have also addressed how to achieve co-location of an attacker instance with a victim instance in these PaaS clouds. To our knowledge, our attacks are thus the first granular, cross-tenant attacks demonstrated on commercial clouds, PaaS or otherwise.

A key ingredient in our attacks is a framework we develop through which the attacker instance can trace a victim's execution paths inside shared executables. Starting with the control-flow graph (CFG) of a executable shared with the victim, our framework consists of building an *attack nondeterministic* finite automaton (attack NFA) that prescribes the memory chunks that the attack instance should monitor over time, using a known cache-based side channel (Gullasch et al., 2011; Yarom and Falkner, 2013), in order to trace the victim's execution path in the CFG. This general framework can then be used to characterize the victim's execution for specific attacks, such as the exact number of times a certain execution path segment was traversed in a short interval (in the first attack above); the precise time at which certain path segments were traversed by the victim (as in the second attack); or the direction taken in a specific branch of interest (in the third attack). We believe the attack NFA framework that we introduce here will be similarly useful in subsequent work on both evaluating and defending against cross-instance side-channel attacks. The contributions of the work described in Chapter 6 will be threefold: (i) a general framework for expressing and guiding cross-instance side-channel attacks leveraging shared executables; (ii) identification of novel and important targets for side-channel attacks in PaaS environments; and (iii) demonstration of attacks against these targets in commercial PaaS clouds.

### **CHAPTER 2: BACKGROUND AND PRIOR WORK**

This dissertation revolves around side channels in modern CPU caches and their applications in the context of cloud computing. In this chapter, we will first introduce the background knowledge of CPU cache architectures and cryptographic side channels in CPU caches. Then we will briefly introduce the concept of cloud computing and side-channel threats in the cloud context. We will also summarize the related work on side channels along with the background introduction.

## 2.1 Cryptographic Side Channels in CPU Caches

#### 2.1.1 Caches in Modern Architectures

Modern CPU micro-architectures extensively make use of hardware caches to speed up expensive operations. The hardware caches on an x86 platform may include data caches, instruction caches, translation lookaside buffers, trace caches, branch target buffers (BTB) in the branch prediction unit, etc. The most commonly known caches are data and instruction caches sitting between the processor cores and the main memory, establishing a storage hierarchy in which each level stores the interim data for the next level storage system for quick reference. While current main memory latencies are on the order of several hundred nanoseconds, the fastest L1 cache has latency as low as several nanoseconds, resulting in a difference of two to three orders of magnitude. To reduce the cost of L1 cache misses, current processors include larger L2 and sometimes even L3 caches with slightly higher access latencies.

Cache sizes range from several KB to several MB. They are organized as a sequence of blocks called *cache lines*, with fixed size typically between 8 and 512 bytes. We define a *chunk* as a cacheline-sized, aligned region in the memory. For example, if a cache-line is of size 64B, then each address that is a multiple of 64 defines the chunk starting at that address. Typical caches are *set-associative*. Each chunk in the main memory can be placed into only one cache set to which it maps, but can be placed in any of the w lines in that set. The spectrum of set-associative caches

includes two extremes: *direct-mapped* caches in which each set contains only one cache line and thus a chunk has a unique location in the cache, and *fully associative* caches in which there is only one cache set containing all cache lines—a chunk can be mapped to any location in the cache. Increasing the degree of associativity usually decreases the cache miss rate, but it increases the cost of searching a chunk in the cache.

A w-way set-associative cache is partitioned into m sets, each with w lines of size b. So, if the size of the cache is denoted by c, we have  $m = c/(w \times b)$ . For example, in the L1 instruction cache of an Intel Yorkfield processor as used in our lab testbed, c = 32KB, w = 8, and b = 64B. Hence,  $m = c/(w \times b) = 64$ . Moreover, the number of chunks in a 4KB memory page is 4KB/b = 64. In such cases, memory chunks with the same offset in a memory page will be mapped to the same cache set in such instruction caches.

**Caches in SMP and SMT architectures.** On multi-core (a.k.a., SMP) architectures, different cores may or may not share a cache. For example, in the four-core Intel Extreme processor, each core has its own L1 cache and each of the two L2 caches is shared by two cores. In more modern Intel CPUs, a unified L3 cache is shared by all cores, while each core has its L1 data/instruction caches and a unified L2 cache. CPUs supporting simultaneous multi-threading (SMT)<sup>1</sup> allow multiple threads to execute simultaneously on the same CPU core and share the same cache hierarchy. It has been shown in previous research that SMT facilitates CPU-based side channel attacks because two threads can simultaneously use CPU resources (Percival, 2005; Tromer et al., 2010; Aciiçmez, 2007; Aciiçmez et al., 2010, 2007c).We target systems with multi-core configurations without SMT due to their dominance in today's CPU market. A CPU cache in this case is either time-shared by the attacker and victim, or simultaneously shared by the two entities. An example of a time-shared cache is the L1 cache, which can only be shared by two threads running on the same core in turns.

#### 2.1.2 Taxonomy of Cache Side Channels

Side-channel attacks on computer systems and their use to extract cryptographic keys from a victim entity have been studied in a variety of settings. According to the vantage points of the

<sup>&</sup>lt;sup>1</sup>SMT is called hyperthreading in Intel's terminology.

attackers, existing cryptographic side-channel attacks are generally categorized into one of the three classes: time-driven attacks, trace-driven attacks and access-driven attacks.

#### 2.1.2.1 Time-Driven Attacks

A time-driven cryptographic side-channel attack is possible when the *total* execution times of cryptographic operations with a fixed key are influenced by the value of the key, e.g., due to the structure of the cryptographic implementation or due to system-level effects such as cache evictions. This influence can be exploited by a *remote* attacker who can measure many such timings to statistically infer information about the key, e.g., (Kocher, 1996; Brumley and Boneh, 2003; Aciiçmez et al., 2005; Bernstein, 2005; Bonneau and Mironov, 2006; Aciiçmez et al., 2006). More recently, Weiß et al. (2012) mounted time-driven attacks against an embedded uniprocessor device virtualized by the L4 microkernel, but the differences between virtualized and non-virtualized targets in time-driven attacks are not as significant as those in other attack types. Compared to the cross-VM attacks proposed in Chapter 3, their techniques do not translate to the style of attack we pursue or the virtualized SMP environment in which we attempt it.

## 2.1.2.2 Trace-Driven Attacks

A second class of cryptographic side-channel attacks is called trace-driven. These attacks require the attacker to have physical access to the cryptographic system and be able to continuously monitor the execution trace throughout a cryptographic operation. Such execution traces can be generated via power consumption analysis (Kocher et al., 1999; Akkar et al., 2000; Bertoni et al., 2005; Lauradoux, 2005; Aciiçmez and Koç, 2006), fault analysis (Blömer and Seifert, 2003) or electromagnetic analysis (Gandolfi et al., 2001). The ability to continuously monitor the device makes these attacks quite powerful but typically requires physical proximity to the device. In the cloud context, physical access to the target system is unlikely in most attack scenarios.

### 2.1.2.3 Access-Driven Attacks

The third class of side-channel attacks is a access-driven attack, in which the attacker runs a program on the same system that is performing the cryptographic operation of interest. It assumes the attacker has logical access to the system (i.e., the ability to run his own program) and be able to

monitor usage (e.g., via timing) of a shared architectural component, e.g., the data cache (Percival, 2005; Osvik et al., 2006; Neve and Seifert, 2007; Tromer et al., 2010; Gullasch et al., 2011), instruction cache (Aciiçmez, 2007; Aciiçmez et al., 2010), floating-point multiplier (Aciiçmez and Seifert, 2007), or branch-prediction cache (Aciiçmez et al., 2007c,b). The strongest attacks in this class, first demonstrated only recently (Aciiçmez et al., 2010; Gullasch et al., 2011), are referred to as *asynchronous*, meaning that they don't require the attacker to achieve precisely timed observations of the victim by actively triggering victim operations. These attacks leverage CPUs with SMT or the ability to game operating system process schedulers. Our cross-VM side-channel attack described in Chapter 3 is an asynchronous access-driven side-channel attack through CPU caches in virtualized environments that games the hypervisor scheduler from the guest OS.

### 2.1.3 Prime-Probe Protocols

One particular type of access-driven cache side-channel attack is based on PRIME-PROBE protocols. According to the type of caches the attacks are applied to, techniques used to establish a PRIME-PROBE protocol may slightly differ. Two types of cache PRIME-PROBEs will be described: data cache probing and instruction cache probing. We will defer the introduction to another type of access-driven side channels—FLUSH-RELOAD protocols—to Chapter 6.

## 2.1.3.1 Data Cache Probing

Cache-based timing channels have been widely studied in various contexts. In spite of different methodologies employed in constructing these channels, they all exploit the timing difference in access latencies between the cache and main memory. We first consider the cache-based timing channel constructed by measuring the cache load of a monitored entity V that shares a common data cache with the monitoring entity U. A common method for conducting an access-driven cache attack is to PRIME and later PROBE the cache, a so-called PRIME-PROBE protocol, as introduced by Tromer et al. (2010).

PRIME: Entity U fills an entire cache set S by reading memory region M from its own memory space.

IDLE: Entity U waits for a prespecified PRIME-PROBE *interval* while the cache is utilized by monitored entity V.

PROBE: Entity U times the reading of the same memory region M to learn V's cache activity on cache set S.

If there is much cache activity from V during U's PRIME-PROBE interval, then U's data is likely to be evicted from the cache set and replaced with data accessed by V. This will result in a noticeably higher timing measurement in U's PROBE phase than if there had been little activity from V.

Cache-based side channels are typically dependent on the processor architecture and the cache level utilized. In a typical x86 platform, the L1 data caches and the unified L2 or L3 caches can serve as the data cache in the PRIME-PROBE protocol, as they can be loaded via memory reads.

## 2.1.3.2 Instruction Cache Probing

The basic technique for instruction cache probing is similar to that used in data cache probing, except that it times how long it takes to execute instructions from memory associated with individual cache sets, as described previously by Aciiçmez (2007). To do so, we first allocate sufficiently many contiguous memory pages so that their combined size is equal to the size of the I-cache. We then divide each memory page into 64 chunks. The *i*<sup>th</sup> chunk in each page will map to the same cache set. To fill the cache set associated to offset *i*, then, it suffices to execute an instruction within the *i*<sup>th</sup> chunk of each of the allocated pages. Filling a cache set is called PRIME-ing. We will also want to measure the time it takes to fill a cache set, which is called PROBE-ing. To PROBE the cache set associated with offset *i*, we execute the rdtsc instruction, then jump to the first page's *i*<sup>th</sup> chunk, which has an instruction to jump to the *i*<sup>th</sup> chunk of the next page, and so on. The final page jumps back to code that again executes rdtsc and calculates the elapsed time. This is repeated for each of the attacker's VM spies on a victim's VCPU V by measuring the cache load in the L1 instruction cache in the following manner:

PRIME: U fills one or more cache sets by the method described above.

IDLE: U waits for a prespecified PRIME-PROBE *interval* while the cache is utilized by V.

PROBE: U times the duration to refill the same cache sets to learn V's cache activity on those sets.

Cache activity induced by V during U's PRIME-PROBE interval will evict U's instructions from the cache sets and replace them with V's. This will result in a noticeably higher timing measurement in U's PROBE phase than if there had been little activity from V. Of course, PROBE-ing also accomplishes PRIME-ing the cache sets (i.e., evicting all instructions other than U's), and so repeatedly PROBE-ing, with one PRIME-PROBE interval between each PROBE, eliminates the need to separately conduct a PRIME step.

#### 2.1.4 Sources of Noise

The PRIME-PROBE protocols described in previous sections may be subject to many sources of noise, especially in the virtualized environment. We categorize them as hardware noise and software noise.

#### 2.1.4.1 Hardware Noise

**TLB misses.** Most CPUs implement virtual memory as a method of providing a contiguous address space to processes. To speed up address translation, translation lookaside buffers (TLBs) cache recently used page table entries containing virtual-to-physical memory mappings. In x86 processors, hardware TLBs are usually small set-associative caches that cache the translation from virtual addresses to physical addresses. Upon a TLB miss, the CPU itself walks the page tables to look for a mapping of the virtual address not found in the TLB, which can be expensive (as high as 100 cycles). When PROBEing per-core caches that involve context switches, such as L1 data caches or L1 instruction caches, because the TLB is flushed at each context switch, the PROBE of the first cache set will always involve TLB misses and so will be abnormally high; as such, the PROBE results for the first cache set will be discarded. When PROBEing large caches, such as last-level caches, the number of memory pages used for the PRIME-PROBE protocol is usually large which may invoke TLB evictions during the PRIME-PROBE protocols, adding noise in the cache timing measurements.

**Speculative execution and hardware prefetching.** Modern superscalar processors usually fetch instructions in batches and execute them out-of-order. This is an issue for accurate time measurement

as well as for PROBEing the instruction caches. In order to force the in-order execution of our PROBE code for accurate measurement, the instructions need to be serialized using instructions like cpuid and mfence. Data cache misses usually involve hardware prefetching activities. CPUs will prefetch several cache lines from a memory page that incurs several cache misses. To obtain accurate timing measurements in the PROBE phase, one technique is to access the buffer in pseudo-random order in the PROBE phase (Percival, 2005).

**Power saving.** The speed of a PROBE may be subject to change due to CPU power saving modes. If the attacker VM is solely occupying a CPU core, when it finishes its PROBE and relinquishes CPU resources, the core may be slowed to save power. During the PRIME-PROBE protocols, it appears to take longer for the CPU to recover from the power saving mode and, in our experience, yields a much longer effective PRIME-PROBE interval. Thus, longer-then-expected PRIME-PROBE intervals may indicate there was no victim on the same core and so their results are discarded.

#### 2.1.4.2 Software Noise

Emulation of RDTSC instructions. Not all processors maintain a constant-rate timestamp counter (TSC), which means the value of the TSC (from which rdtsc calls are answered) may exhibit nonlinearity under certain conditions, e.g., when enabling Intel SpeedStep technology. Newer generations of Intel processors are equipped with a constant-rate TSC, which maintains a constant rate except when the core is put to sleep. The latest generation of processors come with a so-called invariant TSC, the frequency of which never changes regardless of the state of the processor. In the absence of an invariant TSC, Xen 4.0 or later emulates the rdtsc call to prevent time from going backwards. In this case, the rdtsc call is about 15 or 20 times slower than the native call, which diminishes the attacker VM's ability to measure the duration to PROBE a cache set. In the cross-VM attack described in Section 3, the rdtsc instructions are not emulated, in accordance with our findings in the public clouds, therefore rendering more accurate time measurements.

Noise due to other domains. Xen offers a paravirtualized virtual machine abstraction that requires some changes to the guest operating systems running in each VM. Xen implements a thin hypervisor that controls only basic operations, and a control management virtual machine, dubbed Dom0. To perform privileged operations, guest VMs can issue software traps into the hypervisor, called

hypercalls. Dom0 is responsible for creating and terminating other VMs, configuring some of their parameters, and handling virtual network interfaces and block devices. Both the hypervisor and Dom0 produce cache activity that introduces noise when measuring cache load. For example, to ensure secure partitioning of VMs, Xen validates modifications to guest page tables. Updates to page tables trigger hypercalls into Xen, and thus they induce hypervisor activity that leaves a pattern in the cache. In the PRIME-PROBE protocol, noise from the hypervisor might evict cache lines primed by the monitoring VM and so increase the timings observed in the PROBE phase. Dom0 is responsible for multiplexing I/O devices across different virtual machines. Dom0 implements all device drivers and has access to the network and physical hard drives. All other VMs transfer data through Dom0 using an asynchronous buffering mechanism. Thus, an I/O intensive application triggers significant activity in Dom0, resulting noise in the cache timing measurements.

Address space layout randomization. Address space layout randomization (ASLR) changes the layout of the virtual address space of a program in each execution. Such randomization, in principle, will alter a program's cache patterns from the point of view of side-channel observations. However, it does not interfere with the attack we describe in Section 3 because the L1 cache set to which memory is retrieved is determined purely by its offset in its memory page (see Section 2.1.1), and because ASLR in a Linux implementation aligns libraries to page boundaries. It doesn't affect our side-channel measurements in Section 4 as well, as HomeAlone does not rely on per-cache-set PROBE timing values for co-residency detection.

## 2.2 Cloud Computing and Side-Channel Threats

### 2.2.1 Infrastructure-as-a-Service Clouds

In an IaaS system, computing resources are generally made available to tenants in the form of VM instances. Tenants essentially have complete control of these VMs but no visibility into the lower layers of the infrastructure, e.g., hypervisors (virtual machine monitors) and data-center management consoles. The tenant VM instances may be configured with operating systems from a catalog but are also typically custom-configurable. (Supporting network and storage are often bundled with computing instances but can also be purchased separately.) Amazon's Elastic Compute Cloud (EC2), IBM Computing on Demand, and Rackspace Cloud are well-known examples of IaaS offerings.

Side-channel attacks in the context of infrastructure clouds, or cross-VM settings in general, has been studied in prior work. Demonstrated attacks include side channels by which an attacker VM can extract coarse load measurements of a victim VM with which it is co-located (Ristenpart et al., 2009), and identify pages it shares with a co-located victim VM, allowing it to detect victim VM applications, downloaded files (Suzaki et al., 2011) and its operating system (Owens and Wang, 2011). To the best of our knowledge, the work presented in Chapter 3 is the first demonstrated cryptographic side-channel attack in the cross-VM context.

#### 2.2.2 Platform-as-a-Service Clouds

A canonical public PaaS cloud allows customers to upload interpreted source code (e.g., PHP, Ruby, Node.js, Java) or even application executables, that are then run in a provider-managed host operating system. This OS may itself be running within a guest VM on a public IaaS platform such as Amazon EC2. The host OS facilitates data storage, monitoring and logging, and other value-adds that enable customers to quickly provision applications. A canonical use case is for dynamic web hosting, where the customer provides scripts or applications defining the webpage (i.e., PHP scripts or similar) and a MySQL schema. The convenience and flexibility that PaaS provides to customers, together with the fact that mature IaaS clouds enable quick time-to-market for a new PaaS system, has lead to an explosion in the number of offerings.

#### 2.2.2.1 PaaS Isolation Techniques

PaaS systems are usually multi-tenant, meaning they run multiple customers' instances on the same operating system. As such, isolation between tenants is essential for the security of PaaS clouds. In Table 2.1 we summarize the isolation mechanisms used in a variety of PaaS systems, and describe these models in more detail below.

**Runtime-based isolation.** Some PaaS clouds host applications owned by multiple tenants in the same process and isolate them with application runtimes. Multiple tenants therefore may share, e.g., the same JVM environment and be isolated only by JVM runtime security mechanisms.

**User-based isolation.** A more widely used isolation technique is traditional user-based isolation within the host OS. Each hosted application runs as a non-privileged user on the OS, and the instance

| PaaS cloud                | URL(http://)                                                   | Isolation     |

|---------------------------|----------------------------------------------------------------|---------------|

| AppFog                    | www.appfog.com                                                 | User          |

| Azure                     | azure.microsoft.com                                            | VM            |

| Baidu App Engine          | developer.baidu.com/en                                         | Container     |

| Cloud Foundry             | cloudfoundry.org                                               | User          |

| Elastic Beanstalk         | aws.amazon.com/<br>elasticbeanstalk/                           | VM            |

| Engine Yard               | www.engineyard.com                                             | VM            |

| Heroku                    | www.heroku.com                                                 | Container     |

| HP Cloud Application PaaS | <pre>www.hpcloud.com/products- services/application-paas</pre> | Container     |

| Joyent SmartOS<br>WSO2    | www.joyent.com<br>wso2.com/cloud                               | VM<br>Runtime |

Table 2.1: Example PaaS isolation techniques

is a set of processes run by that user. Basic OS-facilitated memory protection prevents illegal memory accesses across instance boundaries, and correctly configured discretionary access control (DAC) in Unix-like systems prevents cross-instance file accesses.

**Container-based isolation.** The main limitation of user-based isolation is the unrestricted use of computer resources by individual instances. This has been relatively recently addressed with the advent of Linux containers, as implemented by Linux-VServer (linux-vserver.org), OpenVZ (openvz.org), and LXC (linuxcontainers.org). The last has been merged into mainstream Linux kernels. A container is a group of processes that are isolated from other groups via distinct kernel namespaces and CPU scheduling quotas (so-called CPU groups or cgroups).

**VM-based isolation.** Some PaaS clouds give each customer instance a separate IaaS VM instance, thereby leveraging the isolation offered by modern virtualization.

## 2.2.2.2 Side Channels in PaaS

Side-channel attacks in platform clouds are similar in concept to traditional cross-process sidechannel attacks. Most access-driven attacks, e.g., (Percival, 2005; Osvik et al., 2006; Neve and Seifert, 2007; Aciiçmez, 2007; Aciiçmez and Seifert, 2007; Aciiçmez et al., 2007c,b; Tromer et al., 2010; Gullasch et al., 2011; Aciiçmez et al., 2010; Yarom and Falkner, 2013), would, in principle, be applicable in such context. However, for reasons explained in Section 1.4, our proposed attacks in Chapter 6 are so far the only ones demonstrated in public PaaS clouds. Software-based sidechannel information leaks through the procfs file system within an OS have been explored by several researchers (Zhang and Wang, 2009; Jana and Shmatikov, 2012; Qian et al., 2012). In particular, Zhang and Wang (2009) exploited procfs to extract the value of ESP register of another process to perform the inter-keystroke timing analysis. Jana and Shmatikov (2012) used machine learning to infer the web sites being rendered from the number of memory pages owned by the browser process, which is learned by reading /proc/pid/statm. Similarly, Qian et al. (2012) made use of procfs to guess TCP sequence numbers and performed off-path hijacking attacks using them. These attacks were targeting at client-side applications, e.g., guessing user passwords or web contents rendered by a browser, and require sharing of namespaces in Linux kernels, which is prohibited in container-based isolations. Therefore we do not believe this type of software-based side channels can be applied to PaaS clouds in general.

## 2.3 Countermeasures to Side-Channel Attacks

Countermeasures to cache side-channel attacks can be applied to various layers in a computer system. In the context of mitigating cross-VM side channels, prior works can roughly be classified into one of the following categories, based on the layer in which the countermeasure is implemented.

# 2.3.1 Hardware-Layer Approaches

The first category includes proposals of new cache designs by applying the idea of resource partitioning, e.g., (Page, 2005; Wang and Lee, 2006, 2007; Domnitser et al., 2012), or access randomization, e.g., (Wang and Lee, 2007, 2008; Keramidas et al., 2008), to mitigate timing channels in CPU caches on the hardware layer. Other works have proposed approaches to eliminate fine-grained timing sources in hardware designs (Martin et al., 2012). Compared to implementations in other layers, hardware methods usually have lower performance overhead. However, adoption of new hardware techniques is a complex process, which may involve considerations of side effects (e.g., power consumption) and economic feasibility. Therefore, it might take years before these techniques are merged into production and finally used in clouds.

#### 2.3.2 Hypervisor-Layer Approaches

Countermeasures in the second category intend to mitigate cache timing side channels by adapting the hypervisor. One direction along this line is to hide nuances in the program execution time, either by providing a fuzzy timer (Vattikonda et al., 2011) or by forcing all executions to be deterministic (Aviram et al., 2010). However these approaches will exclude many applications that rely on a fine-grained timer from running in the cloud. A conceptually similar but more comprehensive solution is provided by Li et al. (2013), in which all sources of timing channels a VM can observe are identified and categorized; they are mitigated either by aggregating timing events among multiple VM replicas, or by making them deterministic functions of other timing sources. Another direction is to partition the shared resources in the hypervisor (Raj et al., 2009; Shi et al., 2011; Kim et al., 2012). In particular, Raj et al. (2009) statically partition the last level cache (LLC) into several regions and allow VMs to make use of different regions by partitioning physical memory pages accordingly. Kim et al. (2012) improved the performance of this approach by dynamically partitioning the LLCs and extended the protection to L1 caches as well.

## 2.3.3 OS-Layer Approaches

Previous OS-layer approaches were mostly proposed to defend against cross-process sidechannel attacks, e.g., (Percival, 2005; Tromer et al., 2010; Gullasch et al., 2011). To our knowledge, the approach we propose in Chapter 5 is the first to modify the OS layer to mitigate cross-VM side channels.

### 2.3.4 Application-Level Approaches

The last approach is to construct side-channel resistant software implementations. For example, the program counter security model (Molnar et al., 2006; Coppens et al., 2009) eliminates keydependent control flows by transforming the software source code. Other efforts focus on sidechannel free cryptographic implementations e.g., (Könighofer, 2008). These approaches incur significant overheads in some cases (e.g., Coppens et al. (2009) indicate up to  $24\times$ ).

# CHAPTER 3: CROSS-VM CRYPTOGRAPHIC SIDE CHANNELS<sup>1</sup>

In this chapter, we detail our study in cross-VM cryptographic side channels outlined in Section 1.1. We will first give an overview of the proposed attacks and the challenges required to overcome in Section 3.1. From there, a full attack pipeline will be explained in Sections 3.2–3.5. The proposed attacks are then evaluated in a lab environment, which is documented in Section 3.6.

# **3.1** Overview and Challenges

Attack setting. The setting under consideration is the use of confidential data, such as cryptographic keys, in a VM. Our investigations presume an attacker that has in some manner achieved control of a VM co-resident on the same physical computer as the victim VM, such as by compromising an existing VM that is co-resident with the victim.